Global Semiconductor Tester Interface Market Strategic Analysis 2021-2031

- Single User License (1 Users) $ 3,500

- Team License (2~5 Users) $ 4,500

- Corporate License (>5 Users) $ 5,500

EXECUTIVE SUMMARY AND INDUSTRY INTRODUCTION

The global semiconductor industry is undergoing a structural transformation driven by advanced packaging, heterogeneous integration, and the proliferation of high-performance computing. At the critical juncture of semiconductor manufacturing lies the testing phase, a mandatory step to ensure yield, reliability, and functionality. Within this domain, the Semiconductor Tester Interface represents a highly specialized and indispensable segment. By 2026, the global market size for semiconductor tester interfaces is projected to reach a range of 0.8 billion to 1.6 billion USD. Driven by increasing chip complexity and advanced packaging requirements, the market is expected to expand at a compound annual growth rate (CAGR) of 6% to 10% through 2031.

Integrated circuit (IC) packaging and testing are situated downstream in the semiconductor production process. The broader semiconductor value chain is traditionally segmented into upstream equipment and materials, midstream semiconductor production, and downstream semiconductor applications. Semiconductor production itself encompasses design, manufacturing, and packaging and testing. From a product formation perspective, chip design occupies the upstream segment of production, responsible for defining product functionality and circuit architecture. Today, design firms predominantly utilize a fabless model, outsourcing wafer fabrication to dedicated foundries. Following fabrication, outsourced semiconductor assembly and test (OSAT) companies or the in-house testing divisions of integrated device manufacturers (IDMs) execute the final packaging and electrical testing, yielding finished, shippable chips. Ultimately, these finished chips are sold to electronic equipment manufacturers as standard or custom devices for system integration.

In the realm of semiconductor testing, the test head of the automated test equipment (ATE) must be physically and electrically connected to a handler (for packaged parts) or a wafer prober (for bare wafers). The Semiconductor Tester Interface facilitates this critical connection. It serves as the complex electro-mechanical bridge between the device under test (DUT) and the testing machine, enabling the accurate input and output of high-speed, high-fidelity testing signals.

The customer base for semiconductor tester interfaces comprises the entirety of semiconductor manufacturers. Suppliers provide these critical interface systems to IDMs, fabless design houses, foundries, and OSATs. Over the historical evolution of the semiconductor industry, IDMs operated via a vertically integrated model, handling every step from design to final sales. However, over the past two decades, the disaggregated fabless-foundry-OSAT model has achieved prominence. Under this decentralized framework, a critical procurement dynamic has emerged: the specific testing platforms and associated interfaces selected by fabless companies for verification during the initial device design phase are frequently adopted by foundries for sample evaluation and wafer-level testing, and subsequently by OSATs for high-volume post-assembly package testing. Consequently, the decision-making process of the fabless customer serves as the fundamental anchor for tester and interface selection across the entire disaggregated supply chain.

REGIONAL MARKET ANALYSIS

The global deployment of semiconductor tester interfaces is heavily influenced by the geographic concentration of foundries, OSATs, and fabless design hubs.

● Asia-Pacific

The Asia-Pacific region dominates the global semiconductor testing market and is expected to exhibit a robust growth rate in the range of 8% to 12% through 2031. This dominance is primarily driven by the massive concentration of wafer foundries and OSATs in Taiwan, China, as well as significant operations in South Korea, mainland China, and Japan. Taiwan, China serves as the epicenter of advanced semiconductor manufacturing, housing the world's leading foundry and a vast ecosystem of OSATs. South Korea's market is propelled by its global leadership in memory semiconductors, necessitating massive volumes of high-parallelism testing interfaces for DRAM and NAND products. Mainland China is aggressively expanding its mature node manufacturing and domestic OSAT capabilities, creating substantial demand for cost-effective, high-volume tester interfaces. Japan remains a critical player, not only as a consumer of testing interfaces but as a primary source of advanced upstream materials and ATE manufacturing.

● North America

North America is projected to experience a steady growth rate of 5% to 8%. The region's strength lies in its undisputed leadership in fabless semiconductor design. Companies designing complex artificial intelligence accelerators, central processing units, and mobile system-on-chips are headquartered here. Because fabless companies dictate the test protocols and interface specifications that OSATs eventually adopt, North American engineering hubs are the primary battleground for interface design wins. Furthermore, recent legislative efforts aimed at reshoring semiconductor manufacturing are stimulating local demand for testing infrastructure, as new fabrication plants are constructed alongside advanced packaging pilot lines.

● Europe

The European market is anticipated to grow at a rate of 4% to 7%. The semiconductor landscape in Europe is heavily skewed toward automotive, industrial, and power electronics. Consequently, the demand for tester interfaces in this region prioritizes extreme reliability, high-voltage handling capabilities, and wide temperature range testing. As the transition to electric vehicles and renewable energy infrastructure accelerates, European IDMs are requiring highly specialized interfaces capable of safely and accurately testing silicon carbide and gallium nitride power devices.

● South America

South America represents a smaller, emerging market for semiconductor tester interfaces, with an estimated growth rate of 3% to 5%. The region's semiconductor activities are primarily confined to final assembly and testing operations in countries like Brazil, catering to local consumer electronics and automotive supply chains. While advanced node testing is limited, there is a steady baseline demand for standardized testing interfaces used in legacy and consumer-grade ICs.

● Middle East and Africa

The Middle East and Africa region is expected to see a growth rate of 2% to 4%. Israel stands out as a significant technological hub within the region, hosting major R&D and design centers for global semiconductor giants. Similar to North America, the focus here is on design verification and early-stage test engineering rather than high-volume outsourced manufacturing. Meanwhile, emerging state-backed technology investments in the Gulf region may catalyze future specialized semiconductor test environments, though the immediate market scale remains niche.

MARKET SEGMENTATION BY APPLICATION

The technical requirements for a semiconductor tester interface vary drastically depending on the end-use application of the silicon being tested.

● Computing and Communications

This segment represents the most technologically demanding frontier for tester interfaces. It encompasses processors for data centers, high-performance computing (HPC), artificial intelligence (AI) accelerators, and 5G networking chips. These ICs are characterized by enormous transistor counts, high thermal outputs, and the need for ultra-fast data transfer rates. Tester interfaces for this segment must support massive pin counts and utilize advanced materials to prevent signal degradation at high frequencies. Furthermore, the rise of high-bandwidth memory (HBM) integrated via advanced packaging requires specialized interfaces that can test known good die (KGD) before final assembly.

● Automotive

Automotive applications demand a distinct set of interface capabilities, prioritizing extreme durability and environmental resilience. Automotive ICs must comply with stringent standards (such as AEC-Q100), meaning they must be tested at extreme temperature ranges. Tester interfaces utilized in this segment must feature advanced thermal management and robust mechanical contacts that do not deform or degrade under repeated thermal cycling. Additionally, the shift toward electric vehicles necessitates interfaces capable of safely handling high voltages and high currents for traction inverter power modules.

● Industrial

Industrial semiconductors, utilized in factory automation, robotics, and smart grid infrastructure, require long-lifecycle testing solutions. The interfaces used for these applications must accommodate a wide variety of mixed-signal, analog, and digital inputs. Precision is paramount, as industrial sensors and microcontrollers often operate in noisy electrical environments, and the test interface must provide absolute signal isolation to ensure accurate performance characterization.

● Consumer

The consumer electronics segment, driving chips for smartphones, wearables, and smart home appliances, is highly sensitive to the cost of test (CoT). Because consumer chips are produced in massive volumes, tester interfaces are designed for high parallelism, enabling the ATE to test dozens or hundreds of devices simultaneously. The mechanical design of the handler interface and docking systems must support rapid indexing times and high throughput without sacrificing contact yield.

● Display

Display driver ICs (DDICs) require highly specialized testing interfaces due to their unique form factors. DDICs often feature an extremely high number of tightly pitched output channels. Tester interfaces for display applications rely on ultra-fine pitch probe cards and specialized sockets that can reliably contact microscopic pads without causing physical damage to the delicate die.

● Others

Other applications include aerospace, defense, and medical devices, where the volume of chips is relatively low but the cost of failure is catastrophically high. Tester interfaces in these sectors are heavily customized, focusing on comprehensive fault coverage and radiation-hardened testing environments.

SUPPLY CHAIN AND VALUE CHAIN ANALYSIS

The value chain of the semiconductor tester interface market is characterized by a high degree of technical interdependence and stringent precision requirements.

● Upstream Value Chain

The upstream segment consists of raw material and precision component suppliers. Key inputs include advanced printed circuit boards (PCBs) with extremely high layer counts and specialized dielectric materials required for high-frequency signal integrity. Another critical component is the contact mechanism, which includes microscopic pogo pins, conductive elastomers, and precision-machined socket housings. The metallurgical properties of these contacts, often requiring proprietary plating techniques to prevent oxidation and wear, dictate the operational lifespan of the tester interface. Additionally, upstream mechanical suppliers provide the raw metals and pneumatics required for test head manipulators and docking systems.

● Midstream Value Chain

The midstream comprises the semiconductor tester interface manufacturers themselves. These companies act as system integrators and precision engineering firms. They take the specifications from the ATE manufacturer and the fabless chip designer to engineer a custom interface that flawlessly mates the test head to the prober or handler. This involves complex signal integrity simulation, thermal fluid dynamics modeling for active cooling during test, and micron-level mechanical alignment engineering.

● Downstream Value Chain and Advanced Packaging Dynamics

The downstream segment consists of the end-users: IDMs, fabless companies, foundries, and OSATs. Currently, the global advanced packaging industry features two primary categories of participants. The first category comprises vendors with a wafer manufacturing background, such as TSMC, Samsung Electronics, and Intel. The second category consists of companies with an OSAT background, such as ASE and JCET.

The entry of wafer foundries into advanced packaging is fundamentally altering the tester interface market. Foundries leverage their front-end process capabilities to achieve system-level optimization, utilizing advanced packaging as a crucial technological strategy to extend Moore's Law. For example, TSMC's 3D Fabric advanced packaging platform, which includes CoWoS, SoIC, and InFO technologies, targets high-end scenarios like HPC, HBM, and AI accelerators. CoWoS-S can integrate HBM with massive GPU or SoC silicon, demonstrating powerful process synergy.

This shift dramatically complicates the tester interface requirement. When multiple bare dies are integrated onto a silicon interposer, testing can no longer wait until final packaging. Interface manufacturers must provide advanced wafer-level testing interfaces to guarantee Known Good Die (KGD) prior to 3D integration. If a defective die is packaged alongside high-value functioning dies, the entire multi-chip module is ruined. Thus, the interface must bridge the gap between traditional wafer sort and final package test, requiring the mechanical precision of a probe alongside the high-speed functional testing capabilities of a final test socket.

COMPANY PROFILES

The semiconductor tester interface ecosystem involves several specialized players, ranging from broad ATE providers to niche mechanical docking and socket manufacturers.

● Advantest Corporation

Advantest is a dominant global leader in automated test equipment for the semiconductor industry. While primarily known for its ATE platforms, Advantest holds a highly influential position in the tester interface ecosystem. The company designs proprietary test heads, handlers, and interface architectures that third-party vendors must comply with. By offering fully integrated test cells, Advantest ensures that its electrical interfaces, thermal control systems, and mechanical docking mechanisms work in seamless harmony, particularly for high-end memory and SoC testing where signal integrity is paramount.

● Cohu Inc.

Cohu is a critical player in semiconductor test and inspection handlers, micro-electro mechanical system (MEMS) test modules, and test contactors. The company excels in providing the physical interface between the IC and the tester. Cohu's interface solutions are highly regarded in the automotive and industrial sectors, where they provide advanced thermal subsystems capable of testing devices at extreme temperature ranges. Their acquisition of interface-focused subsidiaries has broadened their portfolio to include high-frequency radio frequency (RF) contactors and precision probe pins.

● TSE Co. Ltd.

Based in South Korea, TSE Co. Ltd. is a premier manufacturer of semiconductor interface products. The company specializes in load boards, probe cards, and test sockets. TSE has established a formidable presence in the memory semiconductor market, supplying high-density interface boards that allow for the massive parallel testing of DRAM and NAND flash memory. Their expertise lies in the precise routing of complex, multi-layered PCBs that maintain strict impedance control over long signal paths between the ATE and the device under test.

● ISC. Ltd.

ISC Ltd., also headquartered in South Korea, is globally recognized for its innovation in semiconductor test sockets, particularly its pioneering work with silicone rubber sockets. Unlike traditional pogo-pin sockets, ISC's elastomeric solutions provide excellent high-frequency characteristics and minimize physical damage to the solder balls or pads of the device under test. This technology is highly advantageous for mobile applications and advanced packaging interfaces where pitch distances are exceptionally fine and signal fidelity at high speeds is critical.

● BeLINK Co. Ltd.

BeLINK operates as a specialized provider of customized interface solutions and advanced PCB design for semiconductor testing. The company focuses on the intricate engineering required to bridge specific ATE platforms with complex IC packages. Their core competency revolves around high-speed signal integrity analysis and the manufacturing of bespoke load boards and burn-in boards. BeLINK serves as a vital enabler for fabless design houses that require highly customized interface hardware for the initial validation of novel chip architectures.

● InTest Corporation

InTest Corporation focuses heavily on the mechanical and thermal aspects of the tester interface. The company is renowned for its test head manipulators and docking hardware, which are essential for safely and precisely connecting massive ATE test heads (which can weigh hundreds of kilograms) to delicate wafer probers and handlers. Furthermore, InTest provides highly advanced environmental test chambers and thermal heads, enabling the precise temperature forcing required to validate automotive and aerospace semiconductors directly at the test interface.

● Esmo AG

Esmo AG, a German engineering firm, specializes in specialized system integration, handler solutions, and custom automated test cells. In the tester interface ecosystem, Esmo provides the crucial mechanical automation that presents the device to the test contactor. Their expertise in precision mechanics allows them to develop customized docking interfaces and conversion kits that adapt standard handlers to unique, non-standard semiconductor packages, particularly in the industrial and power electronics sectors prevalent in the European market.

● Reid-Ashman Manufacturing Inc.

Reid-Ashman is a critical supplier of the heavy mechanical infrastructure required in the semiconductor test cell. The company is a global leader in the design and manufacture of test head manipulators and mechanical docking systems. Their interface equipment ensures the exact, repeatable, and safe mating of the ATE test head to the handler or prober. Without the precision engineered, counter-balanced kinematic mechanisms provided by companies like Reid-Ashman, the physical interface between the tester and the device handling equipment would be impossible to maintain at the tolerances required for advanced semiconductor nodes.

OPPORTUNITIES AND CHALLENGES

● Opportunities

The rapid adoption of advanced packaging and chiplet-based architectures represents the most significant growth opportunity for the tester interface market. As Moore's Law slows down, the industry is pivoting to heterogeneous integration, placing multiple dies into a single package. This requires highly sophisticated wafer-level probing interfaces to test individual chiplets before assembly. Furthermore, the explosion of generative AI has catalyzed unprecedented demand for high-bandwidth, high-power silicon. Tester interfaces must evolve to manage massive power delivery networks and dissipate hundreds of watts of heat during the test cycle. Additionally, the geopolitical drive for localized semiconductor supply chains is creating parallel manufacturing ecosystems, multiplying the absolute volume of testing infrastructure required globally.

● Challenges

Despite strong growth drivers, the industry faces severe technical and economic challenges. The foremost technical challenge is physical scaling. As I/O pitches shrink to accommodate higher pin densities in advanced packages, traditional mechanical pogo pins struggle to scale down without becoming dangerously fragile. Furthermore, at extreme operating frequencies, the physical interface itself acts as an antenna, causing crosstalk and signal attenuation that mask the true performance of the chip. Economically, the tester interface market is heavily burdened by R&D costs. Interface providers must develop and validate their mechanical and electrical solutions well before the fabless customer has finalized the silicon design, resulting in high sunk costs. Finally, the supply chain for advanced substrates and precision micro-machining is highly consolidated and prone to bottlenecks, limiting the speed at which interface manufacturers can scale production during cyclical industry upswings.

1.1 Study Scope 1

1.2 Research Methodology 2

1.2.1 Data Sources 2

1.2.2 Assumptions 4

1.3 Abbreviations and Acronyms 6

Chapter 2 Global Semiconductor Tester Interface Market Overview 7

2.1 Market Definition and Segmentations 7

2.2 Global Semiconductor Tester Interface Market Dynamics 8

2.2.1 Market Drivers 8

2.2.2 Market Restraints 9

2.2.3 Market Opportunities 10

2.2.4 Industry Trends 11

2.3 Global Semiconductor Tester Interface Market Size and Forecast (2021-2031) 12

Chapter 3 Industry Chain, Technology and Patent Analysis 13

3.1 Semiconductor Tester Interface Value Chain Analysis 13

3.2 Upstream Raw Materials and Key Components 14

3.3 Downstream Integration and End-User Dynamics 15

3.4 Semiconductor Tester Interface Manufacturing Process 16

3.5 Key Patents and Intellectual Property Landscape 17

3.6 Emerging Technologies in High-Frequency and 3D Packaging Testing 18

Chapter 4 Global Semiconductor Tester Interface Market by Product Type 19

4.1 Market Overview by Product Type 19

4.2 Probe Cards 20

4.3 Test Sockets 21

4.4 Load Boards 22

4.5 Device Interface Boards (DIB) and Others 23

Chapter 5 Global Semiconductor Tester Interface Market by Application 25

5.1 Market Overview by Application 25

5.2 Computing and Communications 26

5.3 Automotive 27

5.4 Industrial 28

5.5 Consumer 29

5.6 Display 29

5.7 Others 30

Chapter 6 Global Semiconductor Tester Interface Market by Region 31

6.1 Global Market Size by Region (2021-2031) 31

6.2 North America Market Size and Forecast 32

6.3 Europe Market Size and Forecast 33

6.4 Asia-Pacific Market Size and Forecast 34

6.5 Rest of the World Market Size and Forecast 36

Chapter 7 North America Semiconductor Tester Interface Market Analysis 37

7.1 North America Market by Product Type 37

7.2 North America Market by Application 38

7.3 United States Market Analysis 39

7.4 Canada Market Analysis 40

7.5 Mexico Market Analysis 41

Chapter 8 Europe Semiconductor Tester Interface Market Analysis 42

8.1 Europe Market by Product Type 42

8.2 Europe Market by Application 43

8.3 Germany Market Analysis 44

8.4 United Kingdom Market Analysis 44

8.5 France Market Analysis 45

8.6 Italy Market Analysis 45

8.7 Rest of Europe Market Analysis 46

Chapter 9 Asia-Pacific Semiconductor Tester Interface Market Analysis 47

9.1 Asia-Pacific Market by Product Type 47

9.2 Asia-Pacific Market by Application 48

9.3 China Market Analysis 49

9.4 Taiwan (China) Market Analysis 49

9.5 Japan Market Analysis 50

9.6 South Korea Market Analysis 51

9.7 Southeast Asia Market Analysis 51

9.8 Rest of Asia-Pacific Market Analysis 52

Chapter 10 Competitive Landscape 53

10.1 Global Market Concentration Ratio (CR4, CR8) 53

10.2 Market Share Analysis of Key Players (2021-2026) 54

10.3 Competitive Stratification (Tier 1, Tier 2, Tier 3) 55

10.4 Mergers, Acquisitions, and Strategic Partnerships 56

10.5 Regional Competitive Advantages 58

Chapter 11 Key Market Players Analysis 59

11.1 Advantest Corporation 59

11.1.1 Company Overview 59

11.1.2 Semiconductor Tester Interface Operations and Financial Data 60

11.1.3 R&D Expenditure and Technology Strategy 61

11.1.4 SWOT Analysis 62

11.2 Cohu Inc. 63

11.2.1 Company Overview 63

11.2.2 Semiconductor Tester Interface Operations and Financial Data 64

11.2.3 R&D Expenditure and Technology Strategy 65

11.2.4 SWOT Analysis 66

11.3 TSE Co. Ltd. 67

11.3.1 Company Overview 67

11.3.2 Semiconductor Tester Interface Operations and Financial Data 68

11.3.3 R&D Expenditure and Technology Strategy 69

11.3.4 SWOT Analysis 70

11.4 ISC. Ltd. 71

11.4.1 Company Overview 71

11.4.2 Semiconductor Tester Interface Operations and Financial Data 72

11.4.3 R&D Expenditure and Technology Strategy 73

11.4.4 SWOT Analysis 74

11.5 BeLINK Co. Ltd. 75

11.5.1 Company Overview 75

11.5.2 Semiconductor Tester Interface Operations and Financial Data 76

11.5.3 R&D Expenditure and Technology Strategy 77

11.5.4 SWOT Analysis 78

11.6 InTest Corporation 79

11.6.1 Company Overview 79

11.6.2 Semiconductor Tester Interface Operations and Financial Data 80

11.6.3 R&D Expenditure and Technology Strategy 81

11.6.4 SWOT Analysis 82

11.7 Esmo AG 83

11.7.1 Company Overview 83

11.7.2 Semiconductor Tester Interface Operations and Financial Data 84

11.7.3 R&D Expenditure and Technology Strategy 85

11.7.4 SWOT Analysis 86

11.8 Reid-Ashman Manufacturing Inc. 87

11.8.1 Company Overview 87

11.8.2 Semiconductor Tester Interface Operations and Financial Data 88

11.8.3 R&D Expenditure and Technology Strategy 89

11.8.4 SWOT Analysis 90

Chapter 12 Global Semiconductor Tester Interface Market Forecast (2027-2031) 91

12.1 Macroeconomic Forecast and Industry Outlook 91

12.2 Global Market Size Forecast by Product Type (2027-2031) 92

12.3 Global Market Size Forecast by Application (2027-2031) 93

12.4 Global Market Size Forecast by Region (2027-2031) 94

Chapter 13 Market Strategy and Strategic Recommendations 95

Table 2 Global Semiconductor Tester Interface Market Size by Product Type (2027-2031) 20

Table 3 Global Semiconductor Tester Interface Market Size by Application (2021-2026) 25

Table 4 Global Semiconductor Tester Interface Market Size by Application (2027-2031) 26

Table 5 Global Semiconductor Tester Interface Market Size by Region (2021-2026) 31

Table 6 Global Semiconductor Tester Interface Market Size by Region (2027-2031) 32

Table 7 North America Semiconductor Tester Interface Market Size by Product Type (2021-2031) 37

Table 8 North America Semiconductor Tester Interface Market Size by Application (2021-2031) 38

Table 9 Europe Semiconductor Tester Interface Market Size by Product Type (2021-2031) 42

Table 10 Europe Semiconductor Tester Interface Market Size by Application (2021-2031) 43

Table 11 Asia-Pacific Semiconductor Tester Interface Market Size by Product Type (2021-2031) 47

Table 12 Asia-Pacific Semiconductor Tester Interface Market Size by Application (2021-2031) 48

Table 13 Global Market Concentration Ratio (CR4, CR8) (2021-2026) 53

Table 14 Key Mergers, Acquisitions, and Partnerships in the Semiconductor Tester Interface Market 56

Table 15 Advantest Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 60

Table 16 Advantest R&D Expenditure and Financial Overview (2021-2026) 61

Table 17 Cohu Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 64

Table 18 Cohu R&D Expenditure and Financial Overview (2021-2026) 65

Table 19 TSE Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 68

Table 20 TSE R&D Expenditure and Financial Overview (2021-2026) 69

Table 21 ISC Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 72

Table 22 ISC R&D Expenditure and Financial Overview (2021-2026) 73

Table 23 BeLINK Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 76

Table 24 BeLINK R&D Expenditure and Financial Overview (2021-2026) 77

Table 25 InTest Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 80

Table 26 InTest R&D Expenditure and Financial Overview (2021-2026) 81

Table 27 Esmo Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 84

Table 28 Esmo R&D Expenditure and Financial Overview (2021-2026) 85

Table 29 Reid-Ashman Semiconductor Tester Interface Revenue, Cost and Gross Profit Margin (2021-2026) 88

Table 30 Reid-Ashman R&D Expenditure and Financial Overview (2021-2026) 89

Figure 1 Global Semiconductor Tester Interface Market Size and YoY Growth (2021-2031) 12

Figure 2 Semiconductor Tester Interface Industry Value Chain 13

Figure 3 Upstream Raw Material Price Trend Analysis (2021-2026) 14

Figure 4 Global Semiconductor Tester Interface Patent Filings by Year (2021-2026) 17

Figure 5 Global Semiconductor Tester Interface Market Share by Product Type (2021 vs 2026) 19

Figure 6 Global Probe Cards Market Size and Forecast (2021-2031) 20

Figure 7 Global Test Sockets Market Size and Forecast (2021-2031) 21

Figure 8 Global Load Boards Market Size and Forecast (2021-2031) 22

Figure 9 Global Device Interface Boards (DIB) Market Size and Forecast (2021-2031) 23

Figure 10 Global Semiconductor Tester Interface Market Share by Application (2021 vs 2026) 25

Figure 11 Global Computing and Communications Application Market Size and Forecast (2021-2031) 26

Figure 12 Global Automotive Application Market Size and Forecast (2021-2031) 27

Figure 13 Global Industrial Application Market Size and Forecast (2021-2031) 28

Figure 14 Global Consumer Application Market Size and Forecast (2021-2031) 29

Figure 15 Global Display Application Market Size and Forecast (2021-2031) 29

Figure 16 Global Semiconductor Tester Interface Market Share by Region (2021 vs 2026) 31

Figure 17 United States Semiconductor Tester Interface Market Size and Forecast (2021-2031) 39

Figure 18 Germany Semiconductor Tester Interface Market Size and Forecast (2021-2031) 44

Figure 19 China Semiconductor Tester Interface Market Size and Forecast (2021-2031) 49

Figure 20 Taiwan (China) Semiconductor Tester Interface Market Size and Forecast (2021-2031) 49

Figure 21 Tier 1, Tier 2, and Tier 3 Companies Market Share (2026) 55

Figure 22 Advantest Semiconductor Tester Interface Market Share (2021-2026) 60

Figure 23 Cohu Semiconductor Tester Interface Market Share (2021-2026) 64

Figure 24 TSE Semiconductor Tester Interface Market Share (2021-2026) 68

Figure 25 ISC Semiconductor Tester Interface Market Share (2021-2026) 72

Figure 26 BeLINK Semiconductor Tester Interface Market Share (2021-2026) 76

Figure 27 InTest Semiconductor Tester Interface Market Share (2021-2026) 80

Figure 28 Esmo Semiconductor Tester Interface Market Share (2021-2026) 84

Figure 29 Reid-Ashman Semiconductor Tester Interface Market Share (2021-2026) 88

Research Methodology

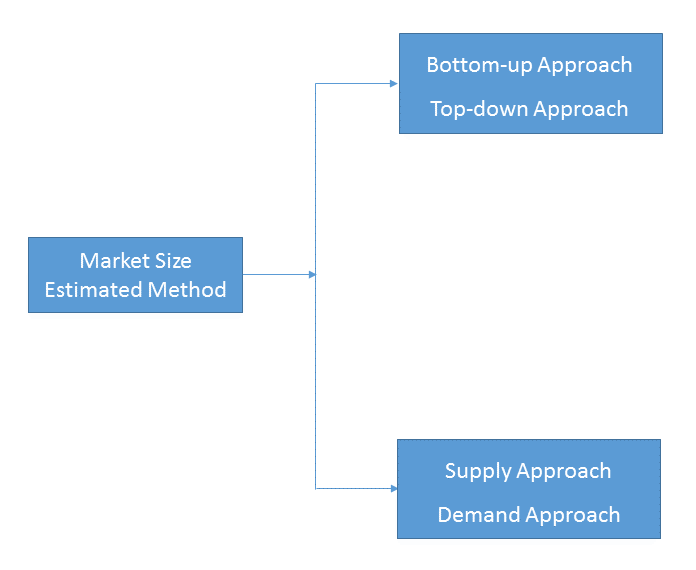

- Market Estimated Methodology:

Bottom-up & top-down approach, supply & demand approach are the most important method which is used by HDIN Research to estimate the market size.

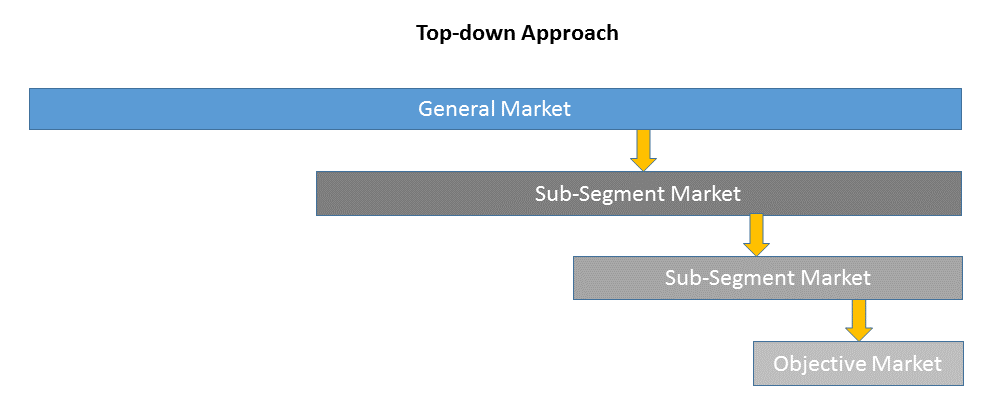

1)Top-down & Bottom-up Approach

Top-down approach uses a general market size figure and determines the percentage that the objective market represents.

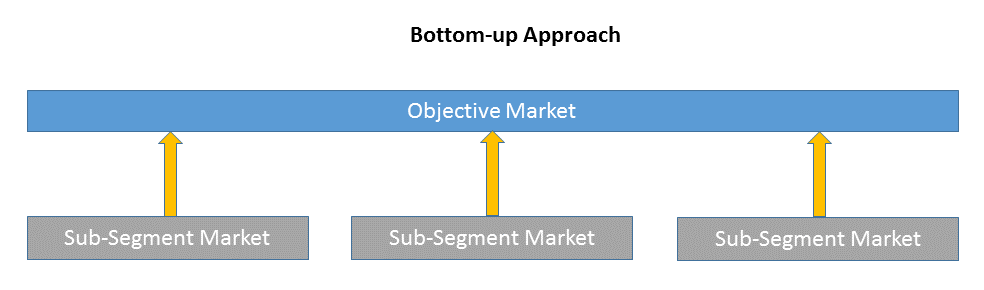

Bottom-up approach size the objective market by collecting the sub-segment information.

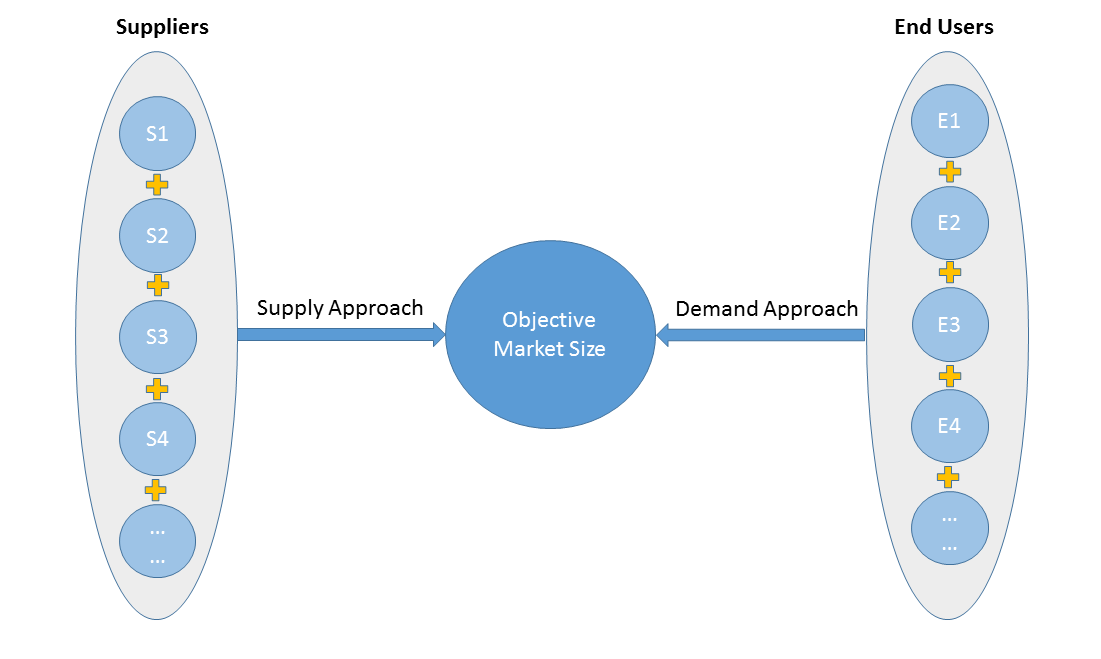

2)Supply & Demand Approach

Supply approach is based on assessments of the size of each competitor supplying the objective market.

Demand approach combine end-user data within a market to estimate the objective market size. It is sometimes referred to as bottom-up approach.

- Forecasting Methodology

- Numerous factors impacting the market trend are considered for forecast model:

- New technology and application in the future;

- New project planned/under contraction;

- Global and regional underlying economic growth;

- Threatens of substitute products;

- Industry expert opinion;

- Policy and Society implication.

- Analysis Tools

1)PEST Analysis

PEST Analysis is a simple and widely used tool that helps our client analyze the Political, Economic, Socio-Cultural, and Technological changes in their business environment.

- Benefits of a PEST analysis:

- It helps you to spot business opportunities, and it gives you advanced warning of significant threats.

- It reveals the direction of change within your business environment. This helps you shape what you’re doing, so that you work with change, rather than against it.

- It helps you avoid starting projects that are likely to fail, for reasons beyond your control.

- It can help you break free of unconscious assumptions when you enter a new country, region, or market; because it helps you develop an objective view of this new environment.

2)Porter’s Five Force Model Analysis

The Porter’s Five Force Model is a tool that can be used to analyze the opportunities and overall competitive advantage. The five forces that can assist in determining the competitive intensity and potential attractiveness within a specific area.

- Threat of New Entrants: Profitable industries that yield high returns will attract new firms.

- Threat of Substitutes: A substitute product uses a different technology to try to solve the same economic need.

- Bargaining Power of Customers: the ability of customers to put the firm under pressure, which also affects the customer's sensitivity to price changes.

- Bargaining Power of Suppliers: Suppliers of raw materials, components, labor, and services (such as expertise) to the firm can be a source of power over the firm when there are few substitutes.

- Competitive Rivalry: For most industries the intensity of competitive rivalry is the major determinant of the competitiveness of the industry.

3)Value Chain Analysis

Value chain analysis is a tool to identify activities, within and around the firm and relating these activities to an assessment of competitive strength. Value chain can be analyzed by primary activities and supportive activities. Primary activities include: inbound logistics, operations, outbound logistics, marketing & sales, service. Support activities include: technology development, human resource management, management, finance, legal, planning.

4)SWOT Analysis

SWOT analysis is a tool used to evaluate a company's competitive position by identifying its strengths, weaknesses, opportunities and threats. The strengths and weakness is the inner factor; the opportunities and threats are the external factor. By analyzing the inner and external factors, the analysis can provide the detail information of the position of a player and the characteristics of the industry.

- Strengths describe what the player excels at and separates it from the competition

- Weaknesses stop the player from performing at its optimum level.

- Opportunities refer to favorable external factors that the player can use to give it a competitive advantage.

- Threats refer to factors that have the potential to harm the player.

- Data Sources

| Primary Sources | Secondary Sources |

|---|---|

| Face to face/Phone Interviews with market participants, such as: Manufactures; Distributors; End-users; Experts. Online Survey |

Government/International Organization Data: Annual Report/Presentation/Fact Book Internet Source Information Industry Association Data Free/Purchased Database Market Research Report Book/Journal/News |