Semiconductor Test Socket Market Strategy 2026-2031

- Single User License (1 Users) $ 3,500

- Team License (2~5 Users) $ 4,500

- Corporate License (>5 Users) $ 5,500

The global semiconductor test socket market is undergoing a structural expansion, exiting its historical position as a commoditized backend consumable to become a primary bottleneck in advanced packaging yield economics. Driven by the aggressive proliferation of Artificial Intelligence (AI) accelerators, High-Bandwidth Memory (HBM), and multi-die packaging paradigms (Chiplet, 2.5D/3D architectures), the financial gravity of the testing ecosystem is shifting. Strategic audits reveal that by 2026, the market valuation will land within an interval of 1.1 billion to 1.9 billion USD, with a forecasted Compound Annual Growth Rate (CAGR) of 6.5% to 9.5% extending through 2031.

This expansion is physically manifested in the rapid densification of chip interfaces. Field intelligence indicates package pin counts are escalating precipitously, frequently breaching 20,000 pins per package for frontier high-performance computing (HPC) modules. Simultaneously, interconnect pitch sizes are compressing down to the 0.25mm to 0.15mm threshold. This simultaneous increase in volume per socket and demand for microscopic precision directly escalates the unit value, driving up the overall Average Selling Price (ASP) across the industry. As fabless entities and Integrated Device Manufacturers (IDMs) push to insulate themselves from multi-thousand-dollar defect costs per advanced chip, test sockets serve as the critical interface securing the Automated Test Equipment (ATE) to the packaged silicon.

REGIONAL MARKET DYNAMICS

The geographic distribution of test socket demand is intricately linked to the regional concentration of frontend fabrication nodes, backend OSAT (Outsourced Semiconductor Assembly and Test) hubs, and fabless design clusters.

● Asia-Pacific (APAC)

APAC remains the unquestioned epicenter of the test socket consumption market, driven by entrenched IDM and OSAT ecosystems. The region's forward-looking growth interval between 7.0% and 10.0%. Taiwan, China represents the highest density of substrate-level and Final Test (FT) socket demand, directly downstream from dominant foundry ecosystems orchestrating CoWoS (Chip-on-Wafer-on-Substrate) packaging. South Korea operates as the absolute baseline for memory IC testing, particularly dictating the burn-in and fine-pitch socket demands for HBM3E and LPDDR architectures. Japan maintains a dominant position in the provision of advanced engineered plastics and precision metal alloys required for socket manufacturing, while also consuming highly specialized sockets for domestic automotive and power electronics testing.

● North America

North American market to expand at an interval of 5.5% to 8.5%. The region's consumption profile is entirely dictated by mega-cap fabless design houses architecting AI accelerators, server CPUs, and network switches. The demand here is highly skewed toward extreme high-pin-count (5,000+ pins) and High-Frequency RF sockets capable of handling vast parallel data processing. Furthermore, nearshoring initiatives and brownfield expansions catalyzed by federal semiconductor subsidies are incentivizing localized test engineering facilities, incrementally shifting prototyping socket demand back to domestic shores.

● Europe

European market growth is structurally constrained to a 4.0% to 6.0% interval, heavily indexed against the automotive, industrial, and power electronics sectors. Silicon Carbide (SiC) and Gallium Nitride (GaN) transition roadmaps among European IDMs necessitate high-current, tri-temperature test sockets. The region relies heavily on Burn-In sockets capable of withstanding punishing thermal cycles to guarantee zero-defect policies for Tier-1 automotive suppliers.

● South America and Middle East & Africa (MEA)

Operating as satellite hubs for legacy node testing and lower-tier OSAT operations, these regions present a growth interval of 2.0% to 4.5%. Capital allocation in these territories remains focused on mature consumer electronics and analog IC testing, utilizing standardized, higher-pitch test sockets with lower barrier-to-entry pricing models.

SUPPLY CHAIN & VALUE CHAIN ARCHITECTURE

Analyzing the ecosystem reveals severe point-source vulnerabilities and distinct zones of value migration. The value chain is segmented into raw material providers, component fabricators, socket integrators, and semiconductor end-users.

● Bottleneck Resilience in Materials

The upstream feedstock is constrained by the availability of high-grade engineering plastics (e.g., PEEK, Torlon, Vespel) required for the socket housing. These polymers must exhibit exceptional dimensional stability under high temperatures and possess precise dielectric constants to prevent signal cross-talk. Concurrently, the metallic alloys used for probes and pogo pins (predominantly beryllium copper and palladium-cobalt alloys) are subject to stringent metallurgical requirements to balance electrical conductivity with mechanical elasticity over hundreds of thousands of insertions. Field intelligence indicates a potential feedstock squeeze in aerospace-grade polymers as aerospace and defense sectors compete for the same raw material base.

● Value Migration at the Integrator Level

Integrators assemble the multi-component modules comprising limit frames, floating plates, drilled plates, and the critical pogo pin or elastomeric arrays. Value is migrating rapidly from the ATE hardware providers toward these consumable socket integrators. Because high-end AI chips require highly customized socket architectures, integrators are securing higher margins by co-designing thermal and electrical interfaces directly with the fabless chip designers months before silicon tape-out.

PRODUCT CLASSIFICATION

Test sockets are highly customized engineering modules, dynamically configured to match the geometric and electrical topology of specific chips.

● Final Test (FT) Sockets

Deployed in the ultimate stages of the backend process, FT sockets verify the electrical functionality and stability of a fully packaged IC. Given the throughput requirements of ATE floors, these sockets require exceptional mechanical durability, often rated for hundreds of thousands of touchdowns. The primary engineering hurdle is maintaining structural integrity and contact resistance stability across multi-site parallel testing.

● Burn-In Test Sockets

Engineered specifically for infant mortality screening, Burn-In sockets stress-test packaged chips under elevated voltage and extreme thermal conditions over extended hours. The critical moats here are material degradation resistance and thermal expansion coefficient matching, ensuring the socket does not warp and lose contact alignment when baked in 125-degree to 150-degree Celsius environments.

● RF / High-Frequency Sockets

Required for 5G, Wi-Fi 7, and radar applications, these sockets utilize specialized coaxial architectures or conductive elastomer technologies to isolate signals. The dominant engineering metric is minimizing insertion loss and preventing signal reflection at high frequencies.

● Substrate-Level Test Sockets

Used to replicate a chip's operational ecosystem on a PCB, these sockets evaluate performance parameters in simulated real-world conditions. They are vital for system-level testing (SLT) of complex SoCs prior to final integration into consumer or enterprise hardware.

TECHNOLOGY DEVELOPMENT TRENDS

The technological evolution of test sockets is strictly tethered to Moore's Law and advanced packaging scaling limitations. Key R&D vectors include:

● High-Frequency & Signal Integrity Optimization

Bandwidth demands are pushing the physical limits of test interfaces. Strategic audits reveal companies are engineering sockets capable of maintaining signal integrity at extreme frequencies. LEENO Industrial has successfully engineered coaxial and RF sockets that satisfy 100GHz bandwidths, achieving high-isolation properties (-60dB) to nullify signal cross-talk. Concurrently, specialized developers like U&U are utilizing advanced elastic bodies and proprietary base materials to secure 16GHz frequency testing while restricting insertion loss to strictly under -1dB.

● Miniaturization and Fine Pitch Geometries

As Chiplet architectures drive I/O bump densities higher, the space between solder balls (pitch) is collapsing. Socket designs are accommodating this via microscopic probe manufacturing. LEENO has commercialized memory sockets for low-power devices with a 0.3mm pitch. Emerging players and divisions within Megatouch and U&U are aggressively developing probe arrays capable of interfacing with fine pitch layouts down to 0.175mm and 0.15mm, requiring photolithographic or advanced MEMS (Micro-Electromechanical Systems) fabrication techniques rather than traditional mechanical machining.

● Advanced Thermal Management Envelopes

The power densities of modern AI accelerators create severe thermal bottlenecks during ATE and Burn-In testing. Without aggressive thermal management, chips will thermally throttle or self-destruct during testing. LEENO has deployed the IDTC (Individual Temperature Control) Burn-in test socket, enabling isolated heating and temperature monitoring for specific Mobile AP chips. Furthermore, cold testing boundaries are expanding; LEENO's Cold Temperature Testing Sockets utilize integrated thermoelectric elements to execute testing at -45 degrees Celsius without relying on massive external thermal chambers. Parallel efforts by U&U are targeting Burn-in components capable of retaining absolute temperature uniformity within a 3-degree Celsius variance while operating inside a 150-degree Celsius zone.

● High Current & Power Capacity Mechanics

The electrification of mobility (EVs) mandates rigorous testing of high-power modules (IGBTs, SiC MOSFETs). Standard pogo pins fuse or melt under high current loads. Market leaders are deploying specialized multi-point contact pins and robust socket architectures capable of sustaining 200A to over 600A, utilizing advanced alloys and proprietary geometric tip designs to minimize contact resistance and manage extreme Joule heating.

DOWNSTREAM APPLICATIONS

● High-Performance Computing (HPC)

This sector consumes the highest ASP sockets. CPUs, GPUs, and AI inference/training accelerators utilize monolithic or multi-die configurations with massive arrays (frequently exceeding 5,000 pins). The sockets demand meticulous impedance matching and force distribution to prevent physical damage to the expensive organic substrates during touchdown.

● Memory ICs

Characterized by high-volume, highly parallel testing protocols. HBM formats, LPDDR series, and dense NAND/NOR flash memory rely on massive socket arrays to test hundreds of chips simultaneously. Cost-per-site and fine-pitch reliability are the dominant procurement criteria for memory OSATs.

● Mobile & Consumer Electronics

Mobile Application Processors (APs), complex camera modules, and 5G Antenna-in-Package (AiP) devices require hybrid testing solutions. High-frequency capability is critical here, driving the adoption of elastomer and coaxial socket variants to test mmWave functionalities without signal degradation.

● Automotive & Power Electronics

Automotive-grade silicon operates on extended lifespan requirements. Tri-temperature test sockets (ranging from deep freezing to extreme heat) are mandatory to qualify ICs for harsh under-hood environments. Power module testing specifically drives the high-current socket sub-segment.

COMPANY PROFILES: STRATEGIC MOATS AND PIVOTS

The competitive landscape is a mix of high-volume legacy providers and hyper-specialized frontier engineering firms.

● LEENO Industrial Inc.

Operating with a massive operational moat in vertical integration, LEENO controls its entire precision machining and plating process. Their strategic pivot toward extreme thermal management (IDTC) and 100GHz coaxial RF arrays positions them as the baseline standard for cutting-edge fabless testing.

● Cohu Inc.

A dominant force in the broader semiconductor testing equipment ecosystem, Cohu leverages its ATE handler footprint to bundle highly customized socket solutions. Their moat lies in the total-cost-of-ownership (TCO) value proposition, providing integrated handler-socket-tester synergies that reduce OSAT setup times.

● ISC Co. Ltd.

Recognized for pioneering silicone rubber-based test sockets, ISC has successfully circumvented traditional pogo-pin mechanical limitations for specific high-frequency memory applications. Their strategic acquisition and material science R&D in elastomeric polymers provide a distinct advantage in fine-pitch memory testing.

● Yokowo Co. Ltd. & NHK Spring Co. Ltd.

Leveraging deep institutional knowledge in metallurgy and precision micro-fabrication from Japan, these entities dominate the supply of specialized micro-contact probes. Their operational moats are built on proprietary plating technologies that drastically extend the insertion lifecycle of high-current test pins.

● WinWay Technology Co. Ltd. & Megatouch Co. Ltd.

WinWay capitalizes on geographical proximity to Taiwan's foundry ecosystem, specializing in extremely high-pin-count sockets for HPC and AI chips. Megatouch is aggressively capturing the fine-pitch arbitrage window, driving development in the sub-0.20mm probe territory critical for next-generation packaging.

● Smiths Group plc (Smiths Interconnect)

A globally diversified engineering entity, Smiths Interconnect provides high-reliability sockets heavily indexed toward RF, aerospace, and defense applications. Their proprietary spring-probe technology ensures stable contact resistance under extreme shock, vibration, and thermal stress.

● TSE Co. Ltd. & Enplas Corporation

TSE continues to expand its footprint in automated burn-in boards and integrated test interfaces, catering heavily to the South Korean memory ecosystem. Enplas leverages extreme precision plastic molding, dominating the burn-in socket housing market where dimensional stability of engineered polymers at high temperatures is paramount.

● Yamaichi Electronics Co. Ltd. & Johnstech International Corporation

Yamaichi maintains a strong portfolio in standardized and custom test sockets, bridging the gap between automotive legacy nodes and high-speed data transmission testing. Johnstech operates with a strict focus on high-performance RF and millimeter-wave contactors, utilizing patented geometries that minimize electrical length and maximize signal fidelity.

● Suzhou UIGreen Micro&Nano Technologies Co. Ltd.

Representing the aggressive localization of the semiconductor supply chain within mainland China, UIGreen utilizes advanced MEMS processing to produce microscopic probes. Their strategic trajectory involves substituting imported high-end sockets for domestic fabless clients navigating geopolitical export controls.

● Other notable entities providing specialized interface geometries, custom thermal hardware, and fine-pitch architecture include Micronics Japan Co. Ltd., Boyd Corporation, Ironwood Electronics Inc., Aries Electronics Inc., Robson Technologies Inc., and Qualmax Inc.

OPPORTUNITIES AND STRUCTURAL INHIBITORS

Through the analytical lens, the test socket market presents a complex matrix of capital arbitrage and physical constraints. Three core structural shifts dictating the next five years of market evolution.

● First, the CapEx to OpEx Substitution Effect in testing ecosystems is accelerating. Historically, fabless companies and OSATs focused their capital allocation on multimillion-dollar ATE mainframes (CapEx). However, as multi-die packages and chiplets become hyper-fragmented, the generic ATE requires highly specific, custom-machined test sockets to interface with each unique chip topology. Test sockets, classified as operational expenditures (OpEx) or consumables, are requiring an increasingly massive share of the Total Cost of Test (TCT). Market players who can transition OSATs into subscription-based or lifecycle-managed socket replacement models will capture outsized, recurring margins.

● Second, Thermal Envelope Arbitrage is superseding pure mechanical durability as the primary competitive battleground. In the sub-3nm era, high-performance logic dies draw unprecedented wattage. When thousands of these chips are tested in parallel on a burn-in board, the aggregate Joule heating can literally melt the surrounding interface architecture. Companies developing active thermal control matrices, micro-fluidic cooling within the socket limits, or thermoelectric sub-chilling (as seen in LEENO's recent architectures) possess a durable technological moat. The physics of heat dissipation, rather than electrical signal continuity, is currently the hardest barrier to scaling test parallelization.

● Finally, the market faces a Structural Yield Paradox related to fine-pitch mechanics. As contact pitches drop from 0.25mm to 0.15mm, the mechanical springs within traditional pogo pins face severe physical limitations regarding force generation and structural integrity. The transition toward stamped MEMS probes or engineered elastomers is mandatory. However, these alternative architectures often suffer from faster material degradation, requiring more frequent replacement cycles. This paradigm forces end-users to balance the necessity of ultra-fine pitch testing against the escalating operational burn rate of test consumables. Strategic capital allocations within this sector must strictly prioritize R&D pipelines focused on advanced material sciences—specifically proprietary beryllium-free alloys and high-resilience conductive polymers—to break this yield-degradation cycle and capture dominance in the 2026-2031 market window.

1.1 Report Overview and Market Boundary Definition 1

1.2 Research Methodology and Data Sourcing Ecosystem 2

1.3 Base Assumptions and Forecasting Models (2021-2031) 4

1.4 Entity Taxonomy and Analytical Abbreviations 5

CHAPTER 2 SEMICONDUCTOR TEST SOCKET ECOSYSTEM ARCHITECTURE 7

2.1 Global Value Chain Configuration and Structural Dynamics 7

2.2 Upstream Advanced Materials and Contact Technologies 9

2.3 Midstream Manufacturing Operations and Yield Metrics 10

2.4 Downstream Fabless and OSAT Integration Paradigms 12

CHAPTER 3 TECHNOLOGICAL PARADIGMS AND PATENT INTELLIGENCE 13

3.1 Evolutionary Trajectory of Pitch Reduction and High-Frequency Testing 13

3.2 Material Science Innovations in Elastomeric and Pogo Pin Structures 15

3.3 Global Patent Landscape and Intellectual Property Moats 16

3.4 Next-Generation Thermal Dissipation Frameworks 18

CHAPTER 4 MARKET DYNAMICS AND MACRO-ECONOMIC TRIGGERS 19

4.1 Global Capacity Expansion in Advanced Packaging Facilities 19

4.2 Supply Chain Resilience and Geo-Economic Shifts 21

4.3 Pricing Architecture and Margin Compressors 23

4.4 Adoption Constraints and Technical Bottlenecks 24

CHAPTER 5 GLOBAL PRODUCT STRATIFICATION AND TRAJECTORY (2021-2031) 25

5.1 Volume and Value Metrics by Product Taxonomy 25

5.2 Final Test (FT) Socket Revenue Matrix and Demand Forecast 27

5.3 Burn-In Test Socket Revenue Matrix and Demand Forecast 29

5.4 RF / High-Frequency Socket Revenue Matrix and Demand Forecast 31

5.5 Substrate-Level Test Socket Revenue Matrix and Demand Forecast 33

CHAPTER 6 DOWNSTREAM APPLICATION PENETRATION AND END-USER ECOSYSTEM 35

5.1 High-Performance Computing (HPC) Demand Drivers and Workloads 35

6.2 Memory ICs Testing Requirements and Market Depth 37

6.3 Mobile and Consumer Electronics Test Cycle Dynamics 39

6.4 Automotive and Power Electronics Reliability Testing 41

6.5 Alternative Verticals and Emerging Silicon Synergies 43

CHAPTER 7 GEOGRAPHIC TOPOLOGY AND REGIONAL LOCALIZATION 45

7.1 Global Regional Volume and Revenue Stratification 45

7.2 North America Advanced Logic Testing Landscape 47

7.3 Europe Automotive and Industrial Semiconductor Dynamics 49

7.4 Asia-Pacific OSAT Concentration and Demand Base 51

7.5 Taiwan (China) Foundry Ecosystem and Test Subcontracting 53

7.6 Rest of World Microelectronics Expansion 55

CHAPTER 8 COMPETITIVE ARCHITECTURE AND MARKET POSITIONING 56

8.1 Tier-1 Vendor Market Share and Oligopolistic Dynamics (2021-2026) 56

8.2 Mergers, Acquisitions, and Ecosystem Consolidation 58

8.3 Vendor Switching Costs and OSAT Procurement Strategies 60

8.4 Global Capacity Footprint of Major Entities 62

CHAPTER 9 CORPORATE INTELLIGENCE FRAMEWORK: NORTH AMERICAN AND EUROPEAN ENTITIES 64

9.1 Cohu Inc. 64

9.1.1 Entity Profile and Strategic Focus 64

9.1.2 SWOT Architecture 65

9.1.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 66

9.1.4 Semiconductor Test Socket Market Share Mapping 67

9.2 Smiths Group plc 68

9.2.1 Entity Profile and Strategic Focus 68

9.2.2 SWOT Architecture 69

9.2.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 70

9.2.4 Semiconductor Test Socket Market Share Mapping 71

9.3 Johnstech International Corporation 72

9.3.1 Entity Profile and Strategic Focus 72

9.3.2 SWOT Architecture 73

9.3.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 74

9.3.4 Semiconductor Test Socket Market Share Mapping 75

9.4 Boyd Corporation 76

9.4.1 Entity Profile and Strategic Focus 76

9.4.2 SWOT Architecture 77

9.4.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 78

9.4.4 Semiconductor Test Socket Market Share Mapping 79

9.5 Ironwood Electronics Inc. 80

9.5.1 Entity Profile and Strategic Focus 80

9.5.2 SWOT Architecture 81

9.5.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 82

9.5.4 Semiconductor Test Socket Market Share Mapping 83

9.6 Aries Electronics Inc. 84

9.6.1 Entity Profile and Strategic Focus 84

9.6.2 SWOT Architecture 85

9.6.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 86

9.6.4 Semiconductor Test Socket Market Share Mapping 87

9.7 Robson Technologies Inc. 88

9.7.1 Entity Profile and Strategic Focus 88

9.7.2 SWOT Architecture 89

9.7.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 90

9.7.4 Semiconductor Test Socket Market Share Mapping 91

CHAPTER 10 CORPORATE INTELLIGENCE FRAMEWORK: ASIAN ENTITIES 92

10.1 Yokowo Co. Ltd. 92

10.1.1 Entity Profile and Strategic Focus 92

10.1.2 SWOT Architecture 93

10.1.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 94

10.1.4 Semiconductor Test Socket Market Share Mapping 95

10.2 LEENO Industrial Inc. 96

10.2.1 Entity Profile and Strategic Focus 96

10.2.2 SWOT Architecture 97

10.2.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 98

10.2.4 Semiconductor Test Socket Market Share Mapping 99

10.3 Megatouch Co. Ltd. 100

10.3.1 Entity Profile and Strategic Focus 100

10.3.2 SWOT Architecture 101

10.3.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 102

10.3.4 Semiconductor Test Socket Market Share Mapping 103

10.4 TSE Co. Ltd. 104

10.4.1 Entity Profile and Strategic Focus 104

10.4.2 SWOT Architecture 105

10.4.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 106

10.4.4 Semiconductor Test Socket Market Share Mapping 107

10.5 WinWay Technology Co. Ltd. 108

10.5.1 Entity Profile and Strategic Focus 108

10.5.2 SWOT Architecture 109

10.5.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 110

10.5.4 Semiconductor Test Socket Market Share Mapping 111

10.6 ISC Co. Ltd. 112

10.6.1 Entity Profile and Strategic Focus 112

10.6.2 SWOT Architecture 113

10.6.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 114

10.6.4 Semiconductor Test Socket Market Share Mapping 115

10.7 Enplas Corporation 116

10.7.1 Entity Profile and Strategic Focus 116

10.7.2 SWOT Architecture 117

10.7.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 118

10.7.4 Semiconductor Test Socket Market Share Mapping 119

10.8 Yamaichi Electronics Co. Ltd. 120

10.8.1 Entity Profile and Strategic Focus 120

10.8.2 SWOT Architecture 121

10.8.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 122

10.8.4 Semiconductor Test Socket Market Share Mapping 123

10.9 NHK Spring Co. Ltd. 124

10.9.1 Entity Profile and Strategic Focus 124

10.9.2 SWOT Architecture 125

10.9.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 126

10.9.4 Semiconductor Test Socket Market Share Mapping 127

10.10 Micronics Japan Co. Ltd. 128

10.10.1 Entity Profile and Strategic Focus 128

10.10.2 SWOT Architecture 129

10.10.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 130

10.10.4 Semiconductor Test Socket Market Share Mapping 131

10.11 Qualmax Inc. 132

10.11.1 Entity Profile and Strategic Focus 132

10.11.2 SWOT Architecture 133

10.11.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 134

10.11.4 Semiconductor Test Socket Market Share Mapping 135

10.12 Suzhou UIGreen Micro&Nano Technologies Co. Ltd. 136

10.12.1 Entity Profile and Strategic Focus 136

10.12.2 SWOT Architecture 137

10.12.3 Semiconductor Test Socket Financials (Revenue, Cost, Gross Margin) 2021-2026 138

10.12.4 Semiconductor Test Socket Market Share Mapping 139

Table 2 Global Patent Filings by Contact Technology Node 2021-2026 17

Table 3 Global Semiconductor Test Socket Revenue by Product Taxonomy 2021-2031 25

Table 4 Final Test (FT) Socket Revenue Matrix 2021-2031 27

Table 5 Burn-In Test Socket Revenue Matrix 2021-2031 29

Table 6 RF / High-Frequency Socket Revenue Matrix 2021-2031 31

Table 7 Substrate-Level Test Socket Revenue Matrix 2021-2031 33

Table 8 High-Performance Computing (HPC) Demand Drivers and Value Generation 2021-2031 36

Table 9 Memory ICs Testing Volume and Structural Revenue 2021-2031 38

Table 10 Mobile and Consumer Electronics Test Cycle Revenue 2021-2031 40

Table 11 Automotive and Power Electronics Test Architecture Revenue 2021-2031 42

Table 12 Global Regional Volume and Revenue Stratification 2021-2031 46

Table 13 North America Advanced Logic Testing Matrix 2021-2031 48

Table 14 Europe Automotive and Industrial Semiconductor Dynamics 2021-2031 50

Table 15 Asia-Pacific OSAT Concentration Metrics 2021-2031 52

Table 16 Taiwan (China) Foundry Ecosystem and Subcontracting Dynamics 2021-2031 54

Table 17 Tier-1 Vendor Global Market Share Metrics 2021-2026 57

Table 18 Cohu Inc. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 66

Table 19 Smiths Group plc Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 70

Table 20 Johnstech International Corporation Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 74

Table 21 Boyd Corporation Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 78

Table 22 Ironwood Electronics Inc. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 82

Table 23 Aries Electronics Inc. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 86

Table 24 Robson Technologies Inc. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 90

Table 25 Yokowo Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 94

Table 26 LEENO Industrial Inc. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 98

Table 27 Megatouch Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 102

Table 28 TSE Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 106

Table 29 WinWay Technology Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 110

Table 30 ISC Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 114

Table 31 Enplas Corporation Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 118

Table 32 Yamaichi Electronics Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 122

Table 33 NHK Spring Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 126

Table 34 Micronics Japan Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 130

Table 35 Qualmax Inc. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 134

Table 36 Suzhou UIGreen Micro&Nano Technologies Co. Ltd. Semiconductor Test Socket Revenue, Cost and Gross Margin (2021-2026) 138

Figure 1 Global Semiconductor Test Socket Ecosystem Integration Dynamics 7

Figure 2 Value Chain Economics and Industry Margin Trajectories 11

Figure 3 Evolutionary Trajectory of Pitch Reduction and Material Innovations 14

Figure 4 Market Dynamics and Macro-Economic Triggers Architecture 20

Figure 5 Final Test (FT) Socket Market Penetration Trajectory 2021-2031 28

Figure 6 Burn-In Test Socket Market Penetration Trajectory 2021-2031 30

Figure 7 RF / High-Frequency Socket Market Penetration Trajectory 2021-2031 32

Figure 8 Substrate-Level Test Socket Market Penetration Trajectory 2021-2031 34

Figure 9 High-Performance Computing (HPC) Downstream Penetration and Processing Loads 37

Figure 10 Geographic Topology and Regional Localization Market Share 2026 47

Figure 11 Global Capacity Footprint and Consolidation of Major Entities 63

Figure 12 Cohu Inc. Semiconductor Test Socket Market Share (2021-2026) 67

Figure 13 Smiths Group plc Semiconductor Test Socket Market Share (2021-2026) 71

Figure 14 Johnstech International Corporation Semiconductor Test Socket Market Share (2021-2026) 75

Figure 15 Boyd Corporation Semiconductor Test Socket Market Share (2021-2026) 79

Figure 16 Ironwood Electronics Inc. Semiconductor Test Socket Market Share (2021-2026) 83

Figure 17 Aries Electronics Inc. Semiconductor Test Socket Market Share (2021-2026) 87

Figure 18 Robson Technologies Inc. Semiconductor Test Socket Market Share (2021-2026) 91

Figure 19 Yokowo Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 95

Figure 20 LEENO Industrial Inc. Semiconductor Test Socket Market Share (2021-2026) 99

Figure 21 Megatouch Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 103

Figure 22 TSE Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 107

Figure 23 WinWay Technology Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 111

Figure 24 ISC Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 115

Figure 25 Enplas Corporation Semiconductor Test Socket Market Share (2021-2026) 119

Figure 26 Yamaichi Electronics Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 123

Figure 27 NHK Spring Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 127

Figure 28 Micronics Japan Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 131

Figure 29 Qualmax Inc. Semiconductor Test Socket Market Share (2021-2026) 135

Figure 30 Suzhou UIGreen Micro&Nano Technologies Co. Ltd. Semiconductor Test Socket Market Share (2021-2026) 139

Research Methodology

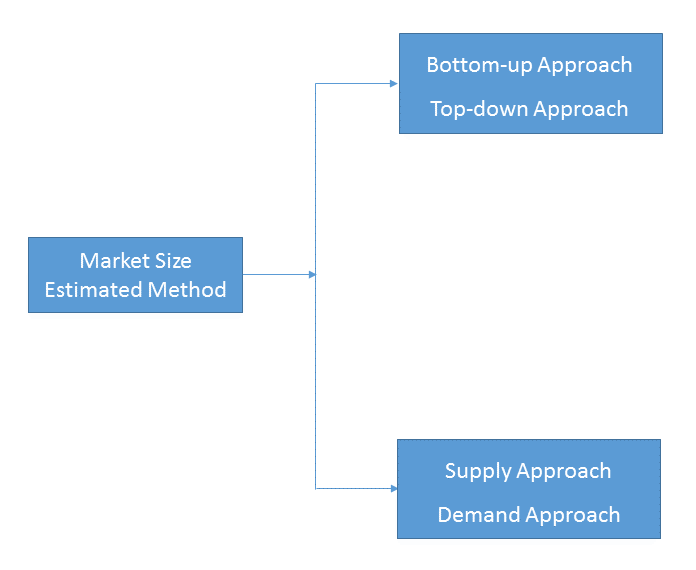

- Market Estimated Methodology:

Bottom-up & top-down approach, supply & demand approach are the most important method which is used by HDIN Research to estimate the market size.

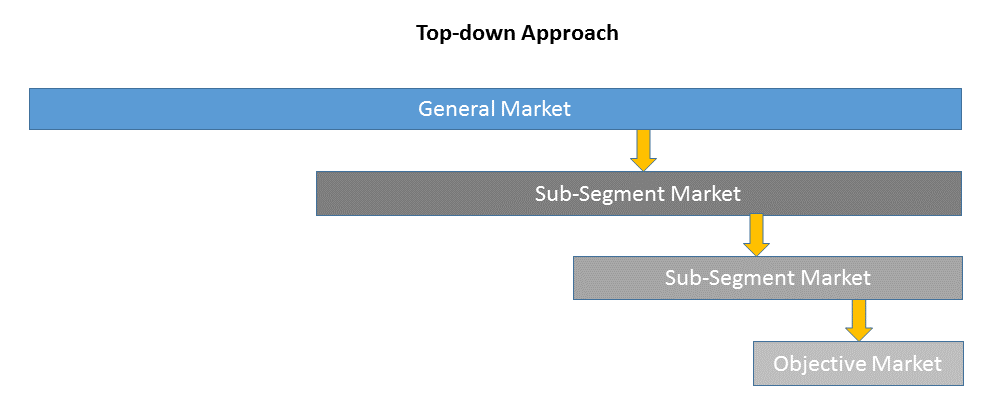

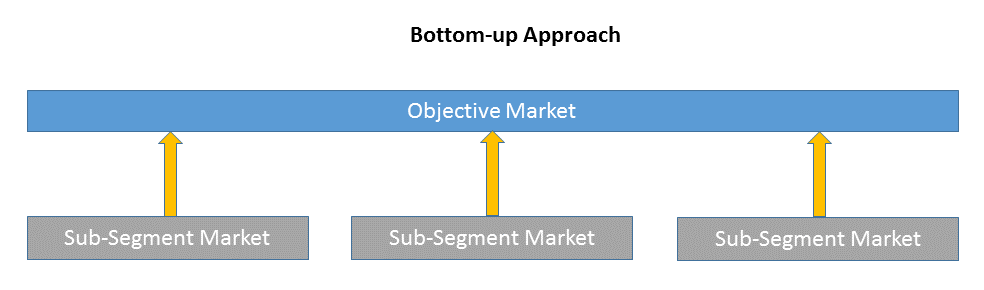

1)Top-down & Bottom-up Approach

Top-down approach uses a general market size figure and determines the percentage that the objective market represents.

Bottom-up approach size the objective market by collecting the sub-segment information.

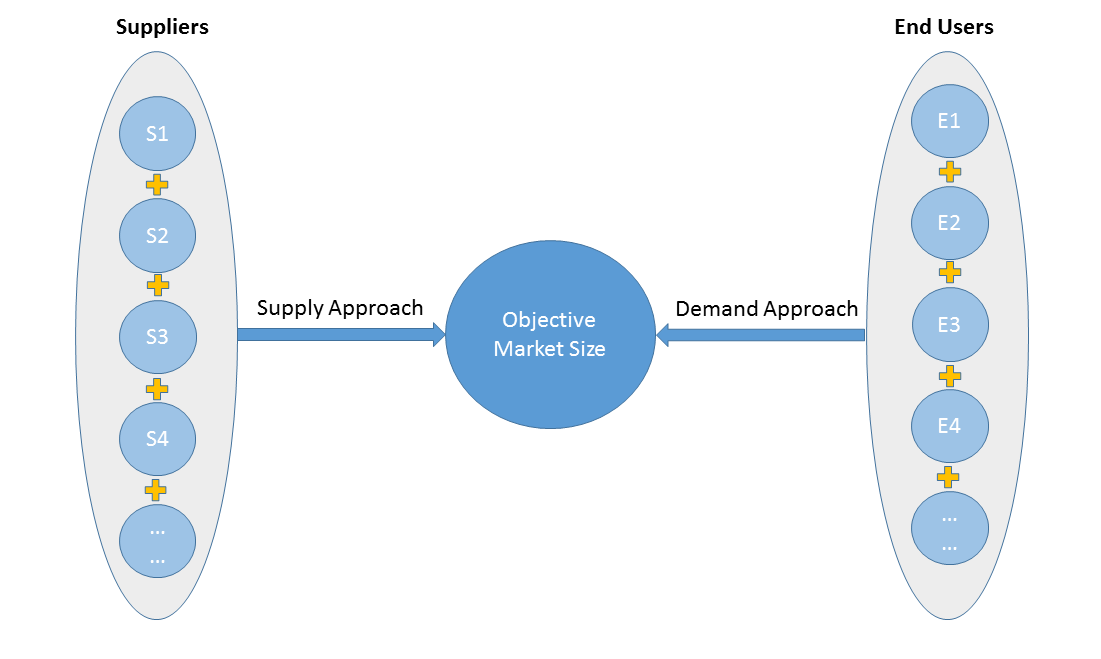

2)Supply & Demand Approach

Supply approach is based on assessments of the size of each competitor supplying the objective market.

Demand approach combine end-user data within a market to estimate the objective market size. It is sometimes referred to as bottom-up approach.

- Forecasting Methodology

- Numerous factors impacting the market trend are considered for forecast model:

- New technology and application in the future;

- New project planned/under contraction;

- Global and regional underlying economic growth;

- Threatens of substitute products;

- Industry expert opinion;

- Policy and Society implication.

- Analysis Tools

1)PEST Analysis

PEST Analysis is a simple and widely used tool that helps our client analyze the Political, Economic, Socio-Cultural, and Technological changes in their business environment.

- Benefits of a PEST analysis:

- It helps you to spot business opportunities, and it gives you advanced warning of significant threats.

- It reveals the direction of change within your business environment. This helps you shape what you’re doing, so that you work with change, rather than against it.

- It helps you avoid starting projects that are likely to fail, for reasons beyond your control.

- It can help you break free of unconscious assumptions when you enter a new country, region, or market; because it helps you develop an objective view of this new environment.

2)Porter’s Five Force Model Analysis

The Porter’s Five Force Model is a tool that can be used to analyze the opportunities and overall competitive advantage. The five forces that can assist in determining the competitive intensity and potential attractiveness within a specific area.

- Threat of New Entrants: Profitable industries that yield high returns will attract new firms.

- Threat of Substitutes: A substitute product uses a different technology to try to solve the same economic need.

- Bargaining Power of Customers: the ability of customers to put the firm under pressure, which also affects the customer's sensitivity to price changes.

- Bargaining Power of Suppliers: Suppliers of raw materials, components, labor, and services (such as expertise) to the firm can be a source of power over the firm when there are few substitutes.

- Competitive Rivalry: For most industries the intensity of competitive rivalry is the major determinant of the competitiveness of the industry.

3)Value Chain Analysis

Value chain analysis is a tool to identify activities, within and around the firm and relating these activities to an assessment of competitive strength. Value chain can be analyzed by primary activities and supportive activities. Primary activities include: inbound logistics, operations, outbound logistics, marketing & sales, service. Support activities include: technology development, human resource management, management, finance, legal, planning.

4)SWOT Analysis

SWOT analysis is a tool used to evaluate a company's competitive position by identifying its strengths, weaknesses, opportunities and threats. The strengths and weakness is the inner factor; the opportunities and threats are the external factor. By analyzing the inner and external factors, the analysis can provide the detail information of the position of a player and the characteristics of the industry.

- Strengths describe what the player excels at and separates it from the competition

- Weaknesses stop the player from performing at its optimum level.

- Opportunities refer to favorable external factors that the player can use to give it a competitive advantage.

- Threats refer to factors that have the potential to harm the player.

- Data Sources

| Primary Sources | Secondary Sources |

|---|---|

| Face to face/Phone Interviews with market participants, such as: Manufactures; Distributors; End-users; Experts. Online Survey |

Government/International Organization Data: Annual Report/Presentation/Fact Book Internet Source Information Industry Association Data Free/Purchased Database Market Research Report Book/Journal/News |