Semiconductor Probe Card Market Analysis & Forecast 2026

- Single User License (1 Users) $ 3,500

- Team License (2~5 Users) $ 4,500

- Corporate License (>5 Users) $ 5,500

The global semiconductor probe card sector is executing a structural break from historical cyclicality, pivoting heavily on the axis of advanced packaging and high-bandwidth memory (HBM). Functioning as the critical electromechanical interface between testing apparatus and un-diced silicon, probe cards represent the highest-value consumable within the Wafer Sort (CP Test) operational phase.

Field intelligence indicates that by 2026, the market will secure a valuation corridor between 3.5 and 5.5 billion USD, mapping a compound annual growth trajectory of 6.5% to 9.5% through 2031. This expansion is not merely volumetric; it is driven by intense value density. The report is observing a structural shortage in high-tier MEMS (Micro-Electromechanical Systems) probe architectures. The transition toward Chiplet and 2.5D/3D topologies mandates strict "Known Good Die" (KGD) protocols, effectively forcing testing procedures leftward in the fabrication timeline.

Market consolidation remains severe. Strategic audits reveal an entrenched oligopoly where the top ten entities command roughly 80% of global revenue. Traditional mechanical cantilever architectures are facing rapid obsolescence, relegated to legacy nodes, while highly parallel, high-frequency MEMS platforms dictate forward-looking capital expenditure.

REGIONAL MARKET DYNAMICS: STRUCTURAL SHIFTS AND ARBITRAGE WINDOWS

● North America: Advanced Logic and Defense Redundancy

The North American theater is characterized by immense capital injection via federal semiconductor initiatives and hyperscaler data center deployments. Demand centers on foundry and logic test architectures, specifically vertical MEMS probe cards capable of interfacing with high-pin-count CPU/GPU clusters. Brownfield fab expansions by domestic IDMs are generating a predictable procurement pipeline. Furthermore, stringent intellectual property and defense-sector supply chain requirements provide a wide economic moat for incumbent domestic suppliers capable of handling classified or proprietary logic architectures. North American growth is modeled in the 7.0% to 8.5% range.

● Asia-Pacific: The Core Manufacturing Nexus

Asia-Pacific dictates global probe card consumption, segmented by highly specialized regional hubs:

Taiwan, China remains the epicenter for advanced packaging testing. The proliferation of CoWoS (Chip-on-Wafer-on-Substrate) production directly correlates with immense MEMS probe card expenditure. Foundries here demand extreme spatial transformer capabilities and 1-Touch Down configurations to maximize throughput on heavily utilized Teradyne and Advantest automated test equipment.

South Korea and Japan represent the memory testing vanguard. Driven by Samsung, SK Hynix, and Kioxia, regional demand is heavily skewed toward DRAM/HBM multi-para testing capabilities.

Mainland China is aggressively capitalizing on a localization arbitrage window. Driven by geopolitical supply chain fragmentation, mainland fab operators are accelerating the qualification of domestic probe cards. Emerging Chinese entities are executing a technological leapfrog, bypassing traditional cantilever R&D and securing joint ventures or indigenous IP to penetrate the 2D/3D MEMS sector. APAC overall will track at a 7.5% to 9.5% CAGR interval.

● Europe: Automotive Power and Extreme Thermal Testing

European consumption logic diverges from the APAC logic/memory dichotomy. The continent's heavy exposure to Tier-1 automotive and industrial sectors necessitates specialized probe setups. The focus is on Silicon Carbide (SiC) and Gallium Nitride (GaN) power semiconductors. Institutional demand centers on vertical and advanced cantilever hybrid cards capable of extreme thermal cycling (-40C to 150C) for wafer-level burn-in protocols, maintaining micro-scale deformation tolerances while carrying large currents (exceeding 1A per pin). European growth is estimated at a steady 5.5% to 7.0%.

● South America and Middle East & Africa (MEA): Emerging Outposts

Though originating from a low baseline, both South America and the MEA region are experiencing baseline growth (4.0% to 6.0%) due to global supply chain diversification. Sovereign wealth funds in the MEA region are beginning to sponsor downstream assembly and test (OSAT) facilities, aiming to capture localized automotive and consumer electronics value. South America continues to serve as an opportunistic OSAT hub for legacy node testing, sustaining a niche market for conventional epoxy-ring cantilever probe cards.

SUPPLY CHAIN AND VALUE CHAIN ARCHITECTURE

The dissection of the value chain exposes highly asymmetric value distribution and pronounced bottleneck resilience challenges.

● The Feedstock Squeeze and Substrate Bottlenecks

The structural foundation of high-end probe cards relies on Multi-Layer Ceramic (MLC) substrates and custom Space Transformers. These components execute the physical pitch translation from the micro-scale logic bumps on the wafer to the macro-scale printed circuit board (PCB) interfaces of the tester. The analysis indicates a severe feedstock squeeze in high-layer-count MLCs, with a handful of Japanese ceramics integrators controlling global supply. Probe card manufacturers who fail to secure long-term capacity agreements in this tier face margin compression and lead-time blowouts.

● Value Migration via MEMS Lithography

Value has definitively migrated from labor-intensive electromechanical assembly to cleanroom lithography. The production of 3D MEMS probes now mimics front-end semiconductor fabrication, utilizing photolithography, deep reactive-ion etching (DRIE), and complex electroplating across multiple sacrificial layers. This creates an impenetrable capital barrier to entry. It is tracked over 150,000 microscopic contacts on a single 300mm substrate at sub-40-micron pitches. The metallurgical mastery required to formulate Tungsten-Rhenium alloys or proprietary palladium-cobalt tips that resist electromigration under high-frequency load is the definitive operational moat.

TECHNOLOGY EVOLUTION: THE PERFORMANCE ENVELOPE

Generational process shrinkage and advanced packaging have violently compressed bump and pad pitches. There are four non-negotiable vectors of capability:

1. Mandatory MEMS Migration: Hand-assembled mechanical probe arrays fail mathematically at modern bump densities. Lithographically grown MEMS probes (both 2D etched and 3D electroplated directly onto substrates) are the absolute baseline for advanced logic and HBM.

2. Ultra-High Parallelism and 1-Touch Down: To amortize skyrocketing test machine hourly depreciation, operators demand total wafer coverage in a single physical touchdown. This necessitates flawless Coefficient of Thermal Expansion (CTE) matching across the entire probe array to prevent microscopic thermal shearing during operation.

3. Signal and Power Integrity at Extreme Frequencies: AI and 6G silicon require testing at previously theoretical frequencies. Top-tier cards now feature 80 GHz millimeter-wave compliance. Emerging players are mastering 56GHz ultra-high-frequency impedance control and 2.4Gbps high-speed transmission thresholds via micro-coaxial shielding designs.

4. Extreme Thermal and Current Loading: For Wafer Burn-In (WBI) applications targeting automotive and AI logic, probes must endure massive thermal stress and sustain Continuous Current Carrying (CCC) capacities exceeding 1A per tip without mechanical fatigue.

PRODUCT CLASSIFICATION MATRIX

This report classifies the addressable market along dual axes: Architectural Base and Silicon Application.

● By Manufacturing Architecture:

* Cantilever Probe Cards: Epoxy-mounted tungsten/rhenium wire arrays on PCBs. Relegated to single-row pad layouts, LCD drivers, and low-tier MCUs. Experiencing a terminal volume decline.

* Vertical Probe Cards: Guide-plate constrained vertical springs interfacing with flip-chip logic arrays. Provides stable contact force and serves as the workhorse for standard non-memory SoC testing.

* MEMS Probe Cards (2D/3D): The definitive growth vector. 2D silicon-etched or 3D electroplated micro-structures providing extreme precision for KGD testing, high-bandwidth memory arrays, and sub-5nm AI logic.

● By Silicon Application:

* Memory Probes: Bifurcated into NAND and DRAM/HBM. DRAM mandates the absolute bleeding edge of high-speed, high-parallelism capability. NAND demonstrates moderate technical demands with steady volume recovery.

* Non-Memory Probes: Encompassing AI logic, CPUs, GPUs, RF modules, and CMOS Image Sensors (CIS). CIS testing specifically requires proprietary non-reflective architectures and optical alignment cavities, creating lucrative micro-niches.

COMPANY PROFILES: STRATEGIC DOSSIERS

The competitive environment is highly stratified, governed by proprietary metallurgical IP and advanced spatial transformation patents.

● Tier 1: Global Oligarchs

FormFactor Inc.: The undisputed hegemon in the advanced logic and MEMS sector. Possesses an insurmountable moat in high-frequency mmWave testing (up to 80 GHz) and dominates the North American IDM pipeline. Their strategic pivot toward highly integrated multi-die testing protocols secures their position in the Chiplet era.

Technoprobe S.p.A.: The European powerhouse. Commands vast market share in advanced SoC and vertical MEMS deployments. Their operational moat centers on proprietary laser-cutting and MEMS growth capabilities tailored for extreme thermal automotive and logic requirements.

Micronics Japan Co. Ltd. (MJC) & Japan Electronic Materials Corporation (JEM): The twin pillars of memory testing. MJC’s grip on advanced DRAM and NAND multi-para probe architecture aligns perfectly with the South Korean and Japanese memory oligopoly. JEM maintains robust market presence via critical supply chain integration in Asian memory fabs.

● Tier 2: Fast-Followers and Regional Dominators

MPI Corporation & Chunghwa Precision Test Tech. Co. Ltd. (CHPT): Key fixtures in Taiwan, China. Heavily integrated into the TSMC foundry ecosystem. CHPT demonstrates exceptional capability in RF and high-speed digital probing, acting as a critical enabler for smartphone AP and baseband silicon testing.

Nidec SV TCL Pte. Ltd. & Feinmetall GmbH: Nidec SV TCL maintains a broad portfolio across analog, mixed-signal, and logic testing. Feinmetall brings precision German engineering to the cantilever and vertical space, dominating industrial and high-power European testing pipelines.

Korea Instrument, TSE, WILL-Technology, Microfriend: The South Korean contingent. Strategically anchored to Samsung and SK Hynix supply chains. Their primary focus remains accelerating yield economics in memory fabs, particularly pushing the boundaries of NAND flash high-parallel testing.

● Tier 3: The Indigenous Acceleration (Mainland China Vanguard)

Shenzhen DGT Testing Equipment, Suzhou Silicon Test System, Protec Mems Technology, Shenzhen SEICHI Technologies, Suzhou UIGreen Micro&Nano Technologies: This cohort is aggressively capitalizing on sovereign mandates to onshore the semiconductor supply chain. Field intelligence points to significant capital expenditure by these entities into 2D/3D MEMS photolithography cleanrooms. UIGreen and SEICHI are breaching the technical threshold for high-speed impedance control and precision vertical probing, directly challenging foreign incumbents in mid-tier logic and legacy node memory testing.

DOWNSTREAM APPLICATION VECTORS

Wafer Sort (CP Test) is the sole battleground for these architectures. Consumption is dictated by four distinct downstream ecosystems:

● High-Bandwidth Memory (HBM) and Advanced Packaging:

The integration of 2.5D/3D Chiplets means one defective die (bad KGD) nullifies the value of an assembled multi-die package, destroying thousands of dollars in a single failure. This dynamic shifts test intensity to the raw wafer stage. HBM's extreme via density necessitates probe cards capable of unprecedented touchdown precision, representing the most lucrative growth vector in the sector.

● Foundry & Logic (Compute and Edge):

Server CPUs, AI accelerators, and high-end GPUs dictate demand for high-pin-count vertical MEMS. As data centers upgrade to 400G/800G optical networking, the ASICs driving these systems require hyper-clean signal integrity during wafer sort, isolating suppliers capable of 56G PAM4 electrical profiling.

● Consumer & Automotive Electronics:

Smartphones drive volume in RF and CIS testing, demanding high-frequency calibration and optical alignment protocols. Concurrently, the EV transition is pulling massive volumes of high-current probe configurations to test traction inverters, IGBTs, and SiC MOSFETs under triple-temperature stress protocols.

● Micro-LED/OLED Display Architectures:

An emerging spillover market for advanced probe mechanics. Next-generation XR headsets utilizing Micro-LED substrates require the electro-optical evaluation of thousands of microscopic emitting diodes per square inch. Emerging players (notably within the Chinese ecosystem) are deploying hyper-dense probe arrays to capture this XR hardware testing wave.

THE VIEWPOINT: OPPORTUNITIES AND STRUCTURAL INHIBITORS

The report posits that the semiconductor probe card market is fundamentally misunderstood by generic financial models, which often peg growth linearly to overall wafer starts. "Test Intensity" as the true revenue multiplier.

● The Yield Economics Paradigm:

As the industry pivots to advanced packaging, the financial penalty for a false positive (passing a defective die) or a false negative (rejecting a functional die) at the wafer stage has increased exponentially. IDMs and OSATs over-indexing on high-end MEMS probe architectures not merely to increase throughput, but as a direct insurance policy against catastrophic post-packaging yield failures. The 15% price premium on a top-tier FormFactor or Technoprobe MEMS card is immediately absorbed by the yield recovery on $500 AI compute dies.

● The Structural Inhibitor: Substrate Monopoly:

While capital is freely flowing into MEMS lithography expansions, the ultimate cap on global supply remains the multi-layer ceramic (MLC) space transformer. The synthesis of high-density interconnect ceramics capable of matching silicon CTE at high temperatures is governed by a micro-oligopoly in Japan. Prolonged supply chain frictions here will elongate lead times, severely impacting fab operators relying on just-in-time test consumable delivery.

● The Geopolitical Arbitrage Window:

For mainland Chinese suppliers, the next 36 months represent a critical, non-repeatable window. As Western export controls inadvertently ring-fence the domestic market, mid-tier domestic memory and logic operators are forced to qualify local probe card solutions. The entities that transition fastest from cantilever legacy products to viable 3D MEMS architectures during this artificial vacuum will secure permanent institutional lock-in, emerging as globally competitive forces by the end of the forecast period.

1.1 Global Report Architecture 1

1.2 Data Taxonomy and Verification Matrix 2

1.3 Geopolitical and Macroeconomic Assumptions 4

1.4 Nomenclature and Abbreviations 5

Chapter 2 Ecosystem Architecture and Value Chain Dynamics 6

2.1 Upstream Raw Materials Configuration (Ceramic Substrates, Tungsten/Rhenium Alloys) 6

2.2 Core Manufacturing and Assembly Nodes 9

2.3 Downstream Semiconductor Testing Integration 12

2.4 Margin Distribution Across Value Nodes 14

Chapter 3 Technological Evolution and Patent Landscaping 16

3.1 Shift towards Fine Pitch and High Pin Count Testing 16

3.2 Advanced MEMS Fabrication Paradigm Shift 19

3.3 Global Patent Citation Network (2021-2026) 22

Chapter 4 Global Market Trajectory (2021-2031) 24

4.1 Historical Baseline and 2026 Calibrations 24

4.2 Global Revenue Matrix 25

4.3 Global Volume Metrics 27

4.4 Pricing Volatility and Margin Pressures 29

Chapter 5 Product Topology and Penetration Vectors 31

5.1 Cantilever Probe Card Penetration and Dynamics 31

5.2 Vertical Probe Card Penetration and Dynamics 34

5.3 MEMS Probe Card Penetration and Dynamics 37

Chapter 6 Application Verticals and Demand Matrix 40

6.1 High-bandwidth Memory (HBM) 40

6.2 Advanced Packaging 43

6.3 Foundry and Logic 46

6.4 Consumer Electronics 48

6.5 Automotive Electronics 50

6.6 Micro-LED/OLED 52

6.7 Secondary Applications 54

Chapter 7 North America Geostrategic Market Configuration 55

7.1 Regional Market Dynamics 55

7.2 United States 57

7.3 Canada 59

Chapter 8 Europe Geostrategic Market Configuration 60

8.1 Regional Market Dynamics 60

8.2 Germany 61

8.3 Netherlands 62

8.4 United Kingdom 63

Chapter 9 Asia-Pacific Geostrategic Market Configuration 64

9.1 Regional Market Dynamics 64

9.2 Taiwan (China) 66

9.3 South Korea 68

9.4 Japan 70

9.5 China 72

9.6 Southeast Asia 74

Chapter 10 Competitive Architecture and Corporate Intelligence 76

10.1 FormFactor Inc. 76

10.1.1 Corporate Profile and Strategic Posture 76

10.1.2 SWOT Matrix Analysis 77

10.1.3 Semiconductor Probe Card Financials 78

10.1.4 Global Go-to-Market Strategy 79

10.2 Technoprobe S.p.A. 80

10.2.1 Corporate Profile and Strategic Posture 80

10.2.2 SWOT Matrix Analysis 81

10.2.3 Semiconductor Probe Card Financials 82

10.2.4 Global Go-to-Market Strategy 83

10.3 Micronics Japan Co. Ltd. 84

10.3.1 Corporate Profile and Strategic Posture 84

10.3.2 SWOT Matrix Analysis 85

10.3.3 Semiconductor Probe Card Financials 86

10.3.4 Global Go-to-Market Strategy 87

10.4 Japan Electronic Materials Corporation 88

10.4.1 Corporate Profile and Strategic Posture 88

10.4.2 SWOT Matrix Analysis 89

10.4.3 Semiconductor Probe Card Financials 90

10.4.4 Global Go-to-Market Strategy 91

10.5 Korea Instrument Co. Ltd. 92

10.5.1 Corporate Profile and Strategic Posture 92

10.5.2 SWOT Matrix Analysis 93

10.5.3 Semiconductor Probe Card Financials 94

10.5.4 Global Go-to-Market Strategy 95

10.6 Nidec SV TCL Pte. Ltd. 96

10.6.1 Corporate Profile and Strategic Posture 96

10.6.2 SWOT Matrix Analysis 97

10.6.3 Semiconductor Probe Card Financials 98

10.6.4 Global Go-to-Market Strategy 99

10.7 TSE Co. Ltd. 100

10.7.1 Corporate Profile and Strategic Posture 100

10.7.2 SWOT Matrix Analysis 101

10.7.3 Semiconductor Probe Card Financials 102

10.7.4 Global Go-to-Market Strategy 103

10.8 WILL-Technology Co. Ltd. 104

10.8.1 Corporate Profile and Strategic Posture 104

10.8.2 SWOT Matrix Analysis 105

10.8.3 Semiconductor Probe Card Financials 106

10.8.4 Global Go-to-Market Strategy 107

10.9 STAr Technologies Inc. 108

10.9.1 Corporate Profile and Strategic Posture 108

10.9.2 SWOT Matrix Analysis 109

10.9.3 Semiconductor Probe Card Financials 110

10.9.4 Global Go-to-Market Strategy 111

10.10 Chunghwa Precision Test Tech. Co. Ltd. 112

10.10.1 Corporate Profile and Strategic Posture 112

10.10.2 SWOT Matrix Analysis 113

10.10.3 Semiconductor Probe Card Financials 114

10.10.4 Global Go-to-Market Strategy 115

10.11 AMST Co. Ltd. 116

10.11.1 Corporate Profile and Strategic Posture 116

10.11.2 SWOT Matrix Analysis 117

10.11.3 Semiconductor Probe Card Financials 118

10.11.4 Global Go-to-Market Strategy 119

10.12 Feinmetall GmbH 120

10.12.1 Corporate Profile and Strategic Posture 120

10.12.2 SWOT Matrix Analysis 121

10.12.3 Semiconductor Probe Card Financials 122

10.12.4 Global Go-to-Market Strategy 123

10.13 Micro2nano Co. Ltd. 124

10.13.1 Corporate Profile and Strategic Posture 124

10.13.2 SWOT Matrix Analysis 125

10.13.3 Semiconductor Probe Card Financials 126

10.13.4 Global Go-to-Market Strategy 127

10.14 Microfriend Inc. 128

10.14.1 Corporate Profile and Strategic Posture 128

10.14.2 SWOT Matrix Analysis 129

10.14.3 Semiconductor Probe Card Financials 130

10.14.4 Global Go-to-Market Strategy 131

10.15 MPI Corporation 132

10.15.1 Corporate Profile and Strategic Posture 132

10.15.2 SWOT Matrix Analysis 133

10.15.3 Semiconductor Probe Card Financials 134

10.15.4 Global Go-to-Market Strategy 135

10.16 Micro Square Technology Inc. 136

10.16.1 Corporate Profile and Strategic Posture 136

10.16.2 SWOT Matrix Analysis 137

10.16.3 Semiconductor Probe Card Financials 138

10.16.4 Global Go-to-Market Strategy 139

10.17 NHK Spring Co. Ltd. 140

10.17.1 Corporate Profile and Strategic Posture 140

10.17.2 SWOT Matrix Analysis 141

10.17.3 Semiconductor Probe Card Financials 142

10.17.4 Global Go-to-Market Strategy 143

10.18 Soulbrain SLD Co. Ltd. 144

10.18.1 Corporate Profile and Strategic Posture 144

10.18.2 SWOT Matrix Analysis 145

10.18.3 Semiconductor Probe Card Financials 146

10.18.4 Global Go-to-Market Strategy 147

10.19 Synergie CAD Instruments 148

10.19.1 Corporate Profile and Strategic Posture 148

10.19.2 SWOT Matrix Analysis 149

10.19.3 Semiconductor Probe Card Financials 150

10.19.4 Global Go-to-Market Strategy 151

10.20 WinWay Technology Co. Ltd. 152

10.20.1 Corporate Profile and Strategic Posture 152

10.20.2 SWOT Matrix Analysis 153

10.20.3 Semiconductor Probe Card Financials 154

10.20.4 Global Go-to-Market Strategy 155

10.21 Yokowo Co. Ltd. 156

10.21.1 Corporate Profile and Strategic Posture 156

10.21.2 SWOT Matrix Analysis 157

10.21.3 Semiconductor Probe Card Financials 158

10.21.4 Global Go-to-Market Strategy 159

10.22 Shenzhen DGT Testing Equipment Co. Ltd. 160

10.22.1 Corporate Profile and Strategic Posture 160

10.22.2 SWOT Matrix Analysis 161

10.22.3 Semiconductor Probe Card Financials 162

10.22.4 Global Go-to-Market Strategy 163

10.23 Suzhou Silicon Test System Co. Ltd. 164

10.23.1 Corporate Profile and Strategic Posture 164

10.23.2 SWOT Matrix Analysis 165

10.23.3 Semiconductor Probe Card Financials 166

10.23.4 Global Go-to-Market Strategy 167

10.24 Protec Mems Technology Co. Ltd. 168

10.24.1 Corporate Profile and Strategic Posture 168

10.24.2 SWOT Matrix Analysis 169

10.24.3 Semiconductor Probe Card Financials 170

10.24.4 Global Go-to-Market Strategy 171

10.25 Shenzhen SEICHI Technologies Co. Ltd. 172

10.25.1 Corporate Profile and Strategic Posture 172

10.25.2 SWOT Matrix Analysis 173

10.25.3 Semiconductor Probe Card Financials 174

10.25.4 Global Go-to-Market Strategy 175

10.26 Suzhou UIGreen Micro&Nano Technologies Co. Ltd. 176

10.26.1 Corporate Profile and Strategic Posture 176

10.26.2 SWOT Matrix Analysis 177

10.26.3 Semiconductor Probe Card Financials 178

10.26.4 Global Go-to-Market Strategy 179

Chapter 11 2027-2031 Horizon Forecasting and Strategic Imperatives 180

11.1 Geopolitical Trade Vector Implications 180

11.2 Next-Generation Packaging Trajectories 181

11.3 Enterprise Go-to-Market Adjustments 182

Table 2 Global Semiconductor Probe Card Revenue Forecast by Region (2027-2031) 26

Table 3 Global Semiconductor Probe Card Volume Dynamics by Product Type (2021-2026) 28

Table 4 Global Semiconductor Probe Card Revenue by Application Matrix (2021-2026) 42

Table 5 High-bandwidth Memory (HBM) Probe Card Adoption Index 43

Table 6 North America Semiconductor Probe Card Geostrategic Market Data 56

Table 7 Europe Semiconductor Probe Card Geostrategic Market Data 61

Table 8 Asia-Pacific Semiconductor Probe Card Geostrategic Market Data 65

Table 9 Taiwan (China) Semiconductor Probe Card Macro-Metrics 67

Table 10 China Semiconductor Probe Card Macro-Metrics 73

Table 11 Top 10 Global Players Gross Margin Comparative Analysis 76

Table 12 Key Raw Material Procurement Cost Baseline (2021-2026) 77

Table 13 FormFactor Inc. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 78

Table 14 Technoprobe S.p.A. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 82

Table 15 Micronics Japan Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 86

Table 16 Japan Electronic Materials Corporation Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 90

Table 17 Korea Instrument Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 94

Table 18 Nidec SV TCL Pte. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 98

Table 19 TSE Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 102

Table 20 WILL-Technology Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 106

Table 21 STAr Technologies Inc. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 110

Table 22 Chunghwa Precision Test Tech. Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 114

Table 23 AMST Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 118

Table 24 Feinmetall GmbH Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 122

Table 25 Micro2nano Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 126

Table 26 Microfriend Inc. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 130

Table 27 MPI Corporation Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 134

Table 28 Micro Square Technology Inc. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 138

Table 29 NHK Spring Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 142

Table 30 Soulbrain SLD Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 146

Table 31 Synergie CAD Instruments Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 150

Table 32 WinWay Technology Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 154

Table 33 Yokowo Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 158

Table 34 Shenzhen DGT Testing Equipment Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 162

Table 35 Suzhou Silicon Test System Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 166

Table 36 Protec Mems Technology Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 170

Table 37 Shenzhen SEICHI Technologies Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 174

Table 38 Suzhou UIGreen Micro&Nano Technologies Co. Ltd. Semiconductor Probe Card Revenue, Cost and Gross Margin (2021-2026) 178

Figure 1 Global Semiconductor Probe Card Ecosystem Architecture Mapping 6

Figure 2 Margin Distribution Across Value Nodes 14

Figure 3 Global Patent Citation Network (2021-2026) 22

Figure 4 Cantilever Probe Card Penetration Trajectory 32

Figure 5 Global Semiconductor Probe Card Value Generation 2026 vs 2031 39

Figure 6 FormFactor Inc. Semiconductor Probe Card Market Share (2021-2026) 78

Figure 7 Technoprobe S.p.A. Semiconductor Probe Card Market Share (2021-2026) 82

Figure 8 Micronics Japan Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 86

Figure 9 Japan Electronic Materials Corporation Semiconductor Probe Card Market Share (2021-2026) 90

Figure 10 Korea Instrument Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 94

Figure 11 Nidec SV TCL Pte. Ltd. Semiconductor Probe Card Market Share (2021-2026) 98

Figure 12 TSE Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 102

Figure 13 WILL-Technology Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 106

Figure 14 STAr Technologies Inc. Semiconductor Probe Card Market Share (2021-2026) 110

Figure 15 Chunghwa Precision Test Tech. Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 114

Figure 16 AMST Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 118

Figure 17 Feinmetall GmbH Semiconductor Probe Card Market Share (2021-2026) 122

Figure 18 Micro2nano Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 126

Figure 19 Microfriend Inc. Semiconductor Probe Card Market Share (2021-2026) 130

Figure 20 MPI Corporation Semiconductor Probe Card Market Share (2021-2026) 134

Figure 21 Micro Square Technology Inc. Semiconductor Probe Card Market Share (2021-2026) 138

Figure 22 NHK Spring Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 142

Figure 23 Soulbrain SLD Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 146

Figure 24 Synergie CAD Instruments Semiconductor Probe Card Market Share (2021-2026) 150

Figure 25 WinWay Technology Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 154

Figure 26 Yokowo Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 158

Figure 27 Shenzhen DGT Testing Equipment Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 162

Figure 28 Suzhou Silicon Test System Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 166

Figure 29 Protec Mems Technology Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 170

Figure 30 Shenzhen SEICHI Technologies Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 174

Figure 31 Suzhou UIGreen Micro&Nano Technologies Co. Ltd. Semiconductor Probe Card Market Share (2021-2026) 178

Research Methodology

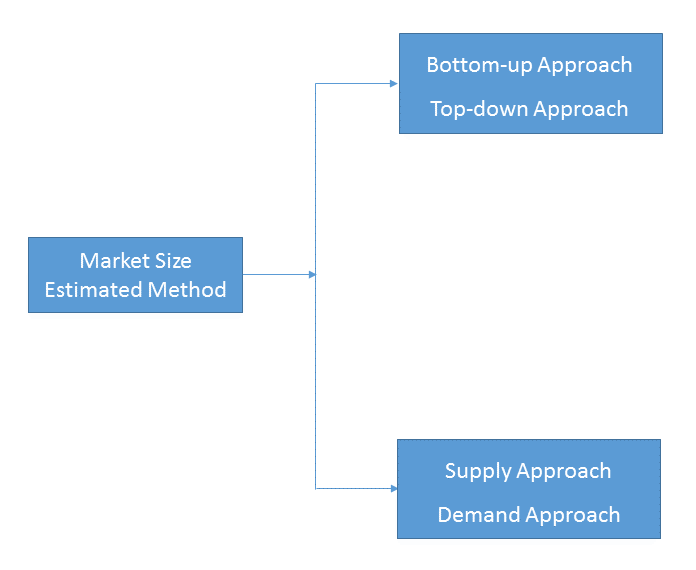

- Market Estimated Methodology:

Bottom-up & top-down approach, supply & demand approach are the most important method which is used by HDIN Research to estimate the market size.

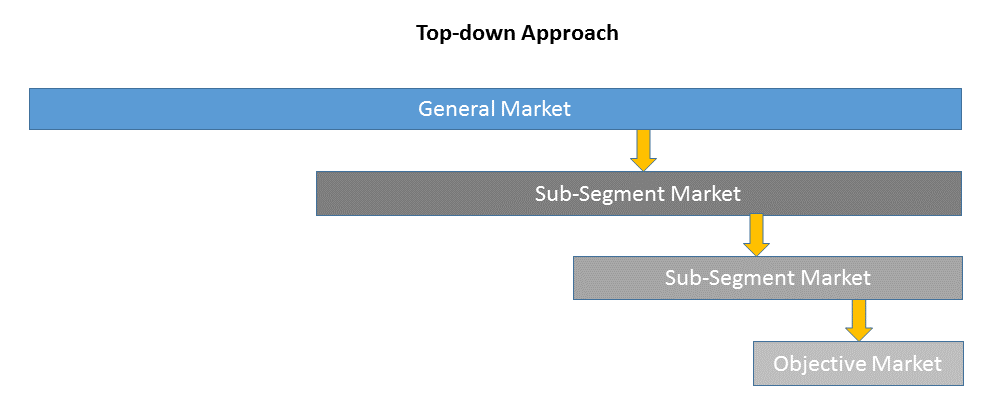

1)Top-down & Bottom-up Approach

Top-down approach uses a general market size figure and determines the percentage that the objective market represents.

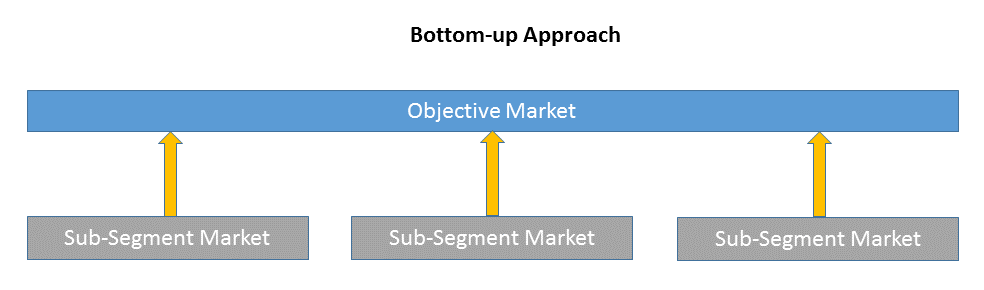

Bottom-up approach size the objective market by collecting the sub-segment information.

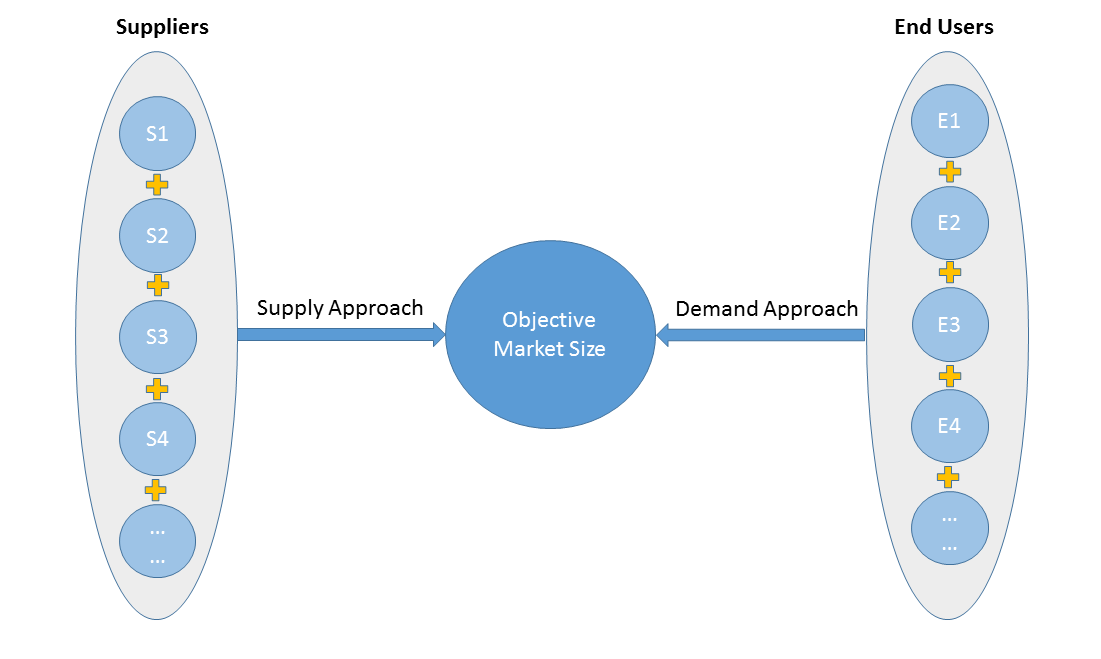

2)Supply & Demand Approach

Supply approach is based on assessments of the size of each competitor supplying the objective market.

Demand approach combine end-user data within a market to estimate the objective market size. It is sometimes referred to as bottom-up approach.

- Forecasting Methodology

- Numerous factors impacting the market trend are considered for forecast model:

- New technology and application in the future;

- New project planned/under contraction;

- Global and regional underlying economic growth;

- Threatens of substitute products;

- Industry expert opinion;

- Policy and Society implication.

- Analysis Tools

1)PEST Analysis

PEST Analysis is a simple and widely used tool that helps our client analyze the Political, Economic, Socio-Cultural, and Technological changes in their business environment.

- Benefits of a PEST analysis:

- It helps you to spot business opportunities, and it gives you advanced warning of significant threats.

- It reveals the direction of change within your business environment. This helps you shape what you’re doing, so that you work with change, rather than against it.

- It helps you avoid starting projects that are likely to fail, for reasons beyond your control.

- It can help you break free of unconscious assumptions when you enter a new country, region, or market; because it helps you develop an objective view of this new environment.

2)Porter’s Five Force Model Analysis

The Porter’s Five Force Model is a tool that can be used to analyze the opportunities and overall competitive advantage. The five forces that can assist in determining the competitive intensity and potential attractiveness within a specific area.

- Threat of New Entrants: Profitable industries that yield high returns will attract new firms.

- Threat of Substitutes: A substitute product uses a different technology to try to solve the same economic need.

- Bargaining Power of Customers: the ability of customers to put the firm under pressure, which also affects the customer's sensitivity to price changes.

- Bargaining Power of Suppliers: Suppliers of raw materials, components, labor, and services (such as expertise) to the firm can be a source of power over the firm when there are few substitutes.

- Competitive Rivalry: For most industries the intensity of competitive rivalry is the major determinant of the competitiveness of the industry.

3)Value Chain Analysis

Value chain analysis is a tool to identify activities, within and around the firm and relating these activities to an assessment of competitive strength. Value chain can be analyzed by primary activities and supportive activities. Primary activities include: inbound logistics, operations, outbound logistics, marketing & sales, service. Support activities include: technology development, human resource management, management, finance, legal, planning.

4)SWOT Analysis

SWOT analysis is a tool used to evaluate a company's competitive position by identifying its strengths, weaknesses, opportunities and threats. The strengths and weakness is the inner factor; the opportunities and threats are the external factor. By analyzing the inner and external factors, the analysis can provide the detail information of the position of a player and the characteristics of the industry.

- Strengths describe what the player excels at and separates it from the competition

- Weaknesses stop the player from performing at its optimum level.

- Opportunities refer to favorable external factors that the player can use to give it a competitive advantage.

- Threats refer to factors that have the potential to harm the player.

- Data Sources

| Primary Sources | Secondary Sources |

|---|---|

| Face to face/Phone Interviews with market participants, such as: Manufactures; Distributors; End-users; Experts. Online Survey |

Government/International Organization Data: Annual Report/Presentation/Fact Book Internet Source Information Industry Association Data Free/Purchased Database Market Research Report Book/Journal/News |